Keysight U7232D DisplayPort Electrical Performance Compliance Test Application

> Methods of Implementation

## Notices

© Keysight Technologies 2007-2016

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

Manual Part Number

U7232-97005

Software Version

3.51.0001

Edition

Eighth Edition, July 2016

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

## Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE. IN FUTURE EDITIONS. FURTHER. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN. INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

# TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

**Technology Licenses**

The hard ware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

## Safety Notices

## CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## DisplayPort Automated Testing-At A Glance

The Keysight U7232D DisplayPort Electrical Performance Compliance Test Application helps you verify compliance of the DisplayPort devices to DisplayPort specifications using Keysight Infiniium Digital Storage Oscilloscopes with bandwidths of 13 GHz or higher. The DisplayPort Electrical Performance Compliance Test Application:

- · Lets you select individual or multiple tests to run.

- · Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- · Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run and lets you specify the thresholds at which marginal or critical warnings appear.

- · Creates a printable HTML report of the tests that have been run.

## NOTE

The tests performed by the DisplayPort Electrical Performance Compliance Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

You may refer to the following specification documents for compliance testing measurements. For more information, see the VESA web site at www.vesa.org.

| Test Specification              | Reference Documents                                                                                                                                             |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DisplayPort 1.3 (1.3)           | VESA DisplayPort (DP) Standard Version 1.3, September 17, 2014                                                                                                  |

| DisplayPort 1.2 (1.2b)          | VESA DisplayPort Standard Version 1, Revision 2a, May 23, 2012<br>VESA DisplayPort PHY Compliance Test Specification Version 1.2b, November 26, 2012            |

| Mobility DisplayPort 1.0 (MyDP) | VESA Mobility DisplayPort (MyDP) Standard Version 1, May 21, 2012<br>VESA Mobility DisplayPort (MyDP) Compliance Test Specification Version 1.0, April 26, 2013 |

| SlimPort (MyDP HBR25)           | SlimPort Compliance Test Specification Version 1, February 28, 2014                                                                                             |

Required Equipment and Software

In order to run the DisplayPort automated tests, you need the following equipment and software:

- Infiniium 90000A Series/90000X Series/90000Q Series/V-Series/Z-Series Digital Storage Oscilloscopes with a bandwidth of 13GHz or higher.

- The minimum version of Infiniium Oscilloscope Software (see the U7232D DisplayPort Compliance Test Application Release Notes).

- U7232D DisplayPort Electrical Performance Compliance Test Application.

- Keyboard, qty = 1, (provided with the Keysight Infiniium oscilloscope).

- Mouse, qty = 1, (provided with the Keysight Infiniium oscilloscope).

- U7232D DisplayPort Electrical Performance Compliance Test Application license.

- N5461B Serial Data Equalization software license (for DisplayPort 1.3 Test Specification only).

- N5465A InfiniiSim Waveform Transformation Toolset license (for DisplayPort 1.3 Test Specification only).

In order to run the automated tests on DisplayPort DUTs, you need the following fixtures and accessories:

• DisplayPort Test Point Adapter:

| For DUT Type  | Required Fixtures/Accessories (Recommended)                                                                                                                                                                                                                                                                                      | Quantity | Recommended Oscilloscope |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|

| Source        | For DisplayPort Type-C Connector N7015A Type-C High-Speed Test Fixture For DisplayPort Connector Wilder Technologies DP-TPA-P* W2641B DisplayPort Test Point Access Adapter For mini DisplayPort Connector Wilder Technologies mDP-TPA-P* Luxshare ICT mDP Plug (mDP-TPA-P)** For MyDP Connector Wilder Technologies MYDP-TPA-P* |          | Infiniium Series         |

| Sink or Cable | For DisplayPort Connector<br>• Wilder technologies DP-TPA-R*<br>For mini DisplayPort Connector<br>• Wilder Technologies mDP-TPA-R*<br>• Luxshare ICT mDP Receptacle (mDP-TPA-R)**<br>For MyDP Connector<br>• Wilder Technologies (MYDP-TPA-R*)                                                                                   |          |                          |

\* All Wilder Technologies Test Point Adapters require the Wilder Technologies DP-TPA-A Aux Control Board.

\*\* All Luxshare ICT Test Point Adapters require the Luxshare ICT DP-TPA-A AUX Control Board.

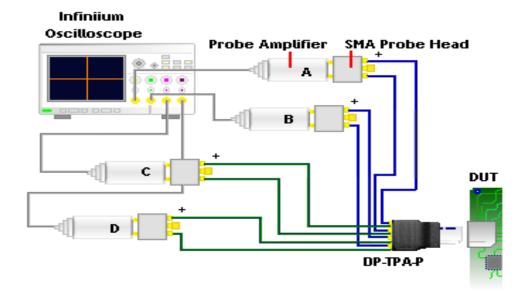

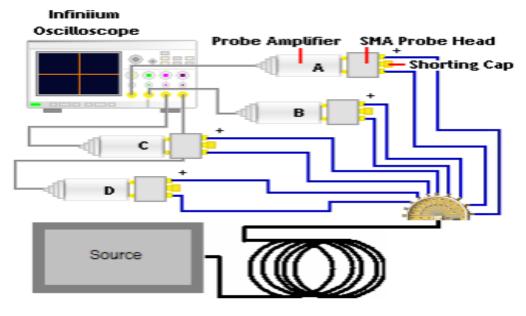

• InfiniiMax Series Probe Amplifiers with minimum 12GHz bandwidth:

| Required Fixtures/Accessories (Recommended)                                                                                                                                                   | Quantity | Recommended Oscilloscope |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|

| <ul> <li>1169A 12GHz InfiniiMax II Series Probe Amplifier</li> <li>N2832A 13GHz InfiniiMax III+ Series Probe Amplifier</li> <li>N2800A 16GHz InfiniiMax III Series Probe Amplifier</li> </ul> | 4        | Infiniium Series         |

• InfiniiMax Series Probe Head with minimum 12GHz bandwidth:

| Test Type            | Required Fixtures/Accessories (Recommended)                                                                                                                                     | Quantity | Recommended Oscilloscope |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|

| Physical Layer Tests | <ul> <li>N5380A InfiniiMax II 12GHz Differential SMA Adapter</li> <li>N5444A InfiniiMax III 28GHz SMA Probe Head</li> </ul>                                                     | 4        |                          |

| AUX Channel Tests    | <ul> <li>E2677A InfiniiMax 12GHz Differential Solder-In<br/>Probe Head</li> <li>E2678A/B InfiniiMax 12GHz<br/>Single-Ended/Differential Probe Head &amp; Accessories</li> </ul> | 1        | Infiniium Series         |

• Other Equipment (required for Internal/Self Calibration of the Infiniium Oscilloscope):

| Required Fixtures/Accessories (Recommended)                  | Quantity | Recommended Oscilloscope/Description                    |

|--------------------------------------------------------------|----------|---------------------------------------------------------|

| BNC to SMA (male) Converter                                  | 4        | Infiniium 90000A Series                                 |

| SMA (male) to SMA (male) Converter                           | 4        | Infiniium 90000X Series/90000Q Series/V-Series/Z-Series |

| E2655A/B/C Probe De-Skew and Performance<br>Verification Kit | 1        | Infiniium Series                                        |

| Calibration Cable                                            | 1        | Infiniium Series                                        |

| 80 $\Omega$ Damping Resistors (01130-81506)                  | 1        | To be used with Socketed Differential Probe Head        |

• Automation Controllers (Optional):

| Testing Type           | Supported Fixtures/Accessories (Optional)                     | Quantity                  | Recommended Oscilloscope |

|------------------------|---------------------------------------------------------------|---------------------------|--------------------------|

| For Source DUT Testing | Unigraf DPR-100 Compact Sized DisplayPort Reference<br>Sink   | 1 (each) Infiniium Series |                          |

| For Sink DUT Testing   | Unigraf DPT-200 Compact Sized DisplayPort Reference<br>Source |                           | mmmum Senes              |

## In This Book

This manual describes the tests that are performed by the DisplayPort Electrical Performance Compliance Test Application in more detail; it contains information from (and refers to) various DisplayPort specifications and it describes how the tests are performed.

- Chapter 1, "Installing the DisplayPort Electrical Performance Compliance Test Application" shows how to install and license the automated test application (if it was purchased separately).

- **Chapter 2**, "Preparing to Take Measurements" shows how to start the DisplayPort Electrical Performance Compliance Test Application and gives a brief overview of how it is used.

- Chapter 3, "DisplayPort 1.2 Source Tests" describes the normative and informative tests for compliance verification of DisplayPort 1.2 source devices.

- Chapter 4, "DisplayPort 1.2 Sink Tests" describes the normative and informative tests for compliance verification of DisplayPort 1.2 sink devices.

- Chapter 5, "DisplayPort 1.2 Cable Tests" describes the normative and informative tests for compliance verification of DisplayPort 1.2 cable devices.

- Chapter 6, "DisplayPort 1.2 AUX Channel Tests" describes the normative and informative AUX channel physical layer tests for compliance verification of DisplayPort 1.2 source and sink devices.

- Chapter 7, "DisplayPort 1.2 Inrush Tests" describes the normative and informative inrush tests for compliance verification of DisplayPort 1.2 source and sink devices as a power consumer.

- **Chapter 8**, "DisplayPort 1.2 Dual Mode Tests" describes the normative and informative Dual Mode physical layer tests for compliance verification of DisplayPort 1.2 source devices.

- Chapter 9, "DisplayPort 1.3 Source Tests" describes the normative and informative tests for compliance verification of DisplayPort 1.3 source devices.

- Chapter 10, "DisplayPort 1.3 Sink Tests" describes the normative and informative tests for compliance verification of DisplayPort 1.3 sink devices.

- Chapter 11, "DisplayPort 1.3 Cable Tests" describes the normative and informative tests for compliance verification of DisplayPort 1.3 cable devices.

- Chapter 12, "DisplayPort 1.3 AUX Channel Tests" describes the normative and informative AUX channel physical layer tests for compliance verification of DisplayPort 1.3 source and sink devices.

- Chapter 13, "DisplayPort 1.3 Inrush Tests" describes the normative and informative inrush tests for compliance verification of DisplayPort 1.3 source and sink devices as a power consumer.

- Chapter 14, "DisplayPort 1.3 Dual Mode Tests" describes the normative and informative Dual Mode physical layer tests for compliance verification of DisplayPort 1.3 source devices.

- Chapter 15, "MyDP 1.0 Source Tests" describes the normative and informative tests for compliance verification of MyDP 1.0 source devices.

- Chapter 16, "MyDP 1.0 Sink Tests" describes the normative and informative tests for compliance verification of MyDP 1.0 sink devices.

- Chapter 17, "MyDP 1.0 Cable Tests" describes the normative and informative tests for compliance verification of MyDP 1.0 cable devices.

- Chapter 18, "MyDP 1.0 AUX Channel Tests" describes the normative and informative AUX channel physical layer tests for compliance verification of MyDP 1.0 source and sink devices.

- Chapter 19, "MyDP 1.0 Inrush Tests" describes the normative and informative inrush tests for compliance verification of MyDP 1.0 source and sink devices as a power consumer.

- Chapter 20, "SlimPort Source Tests" describes the normative and informative tests for compliance verification of SlimPort source devices.

- Chapter 21, "SlimPort Sink Tests" describes the normative and informative tests for compliance verification of SlimPort sink devices.

- Chapter 22, "SlimPort Cable Tests" describes the normative and informative tests for compliance verification of SlimPort cable devices.

- Chapter 23, "SlimPort AUX Channel Tests" describes the normative and informative AUX channel physical layer tests for compliance verification of SlimPort source and sink devices.

- Chapter 24, "SlimPort Inrush Tests" describes the normative and informative inrush tests for compliance verification of SlimPort source and sink devices as a power consumer.

- Chapter 25, "Calibrating the Infiniium Oscilloscope" describes how to calibrate the oscilloscope in preparation for running the DisplayPort automated tests.

- Chapter 26, "InfiniiMax Probing" describes the 1168A/1169A probe amplifier and probe head recommendations for DisplayPort testing.

- Appendix A, "DisplayPort AUX Channel Cookbook for Tx Automated Test" provides a guide on how to implement the test automation features architected in the *DisplayPort Specification 1.1a* using a sink emulator such as the Keysight W2642 DPTC controller.

#### See Also

- The DisplayPort Electrical Performance Compliance Test Application's Online Help, which describes:

- · Starting the DisplayPort Compliance Test Application

- · Creating or Opening a Test Project

- Compliance Limits

- Setting Up the Precision Probe/Cable

- Setting Up Switch Matrix

- Setting Up the Test Environment

- Selecting Tests

- Configuring Tests

- · Connecting the Oscilloscope to the DUT

- · Running Tests

- Automating the Application

- Viewing Results

- Viewing/Exporting/Printing the Report

- Understanding the Report

- Saving Test Projects

- User Defined Add-Ins

- Controlling the Application via a Remote PC

- Using a Second Monitor

#### • DisplayPort References:

| Test Specification              | Reference Documents                                                                                                                                            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DisplayPort 1.3 (1.3)           | VESA DisplayPort (DP) Standard Version 1.3, September 17, 2014                                                                                                 |

| DisplayPort 1.2 (1.2b)          | VESA DisplayPort Standard Version 1, Revision 2a, May 23, 2012<br>VESA DisplayPort PHY Compliance Test Specification Version 1.2b, November 26, 2012           |

| Mobility DisplayPort (MyDP 1.0) | VESA Mobility DisplayPort (MyDP) Standard Version 1, May 21, 2012<br>VESA Mobility DisplayPort (MyDP) Compliance Test Specification Version 1.0, April 8, 2013 |

| SlimPort (MyDP HBR25)           | SlimPort Compliance Test Specification Version 1, February 28, 2014                                                                                            |

# Contents

DisplayPort Automated Testing—At A Glance 3 In This Book 6

## 1 Installing the DisplayPort Electrical Performance Compliance Test Application

**Installing the Software** 48

Installing the License Key 49

## 2 Preparing to Take Measurements

Calibrating the Oscilloscope 52

#### Starting the DisplayPort Electrical Performance Compliance Test Application 53

Online Help Topics 55

## 3 DisplayPort 1.2 Source Tests

## **Overview** 58

Test Point Definition for DisplayPort 1.2 (1.2b) Source Tests61Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.2 Source Tests62Probing/Connection Set Up for DisplayPort 1.2 Source Tests63

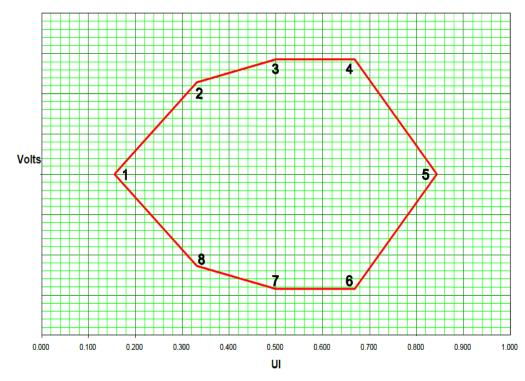

#### Source Eye Diagram Test 64

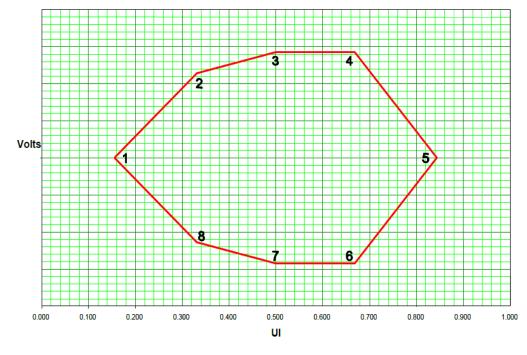

Test ID 64 Test Overview 64 Test Conditions for Eye Diagram Test 64 Test Setup 65 Measurement Procedure 68 PASS Condition 68 Test References 69 Expected/Observable Results 70

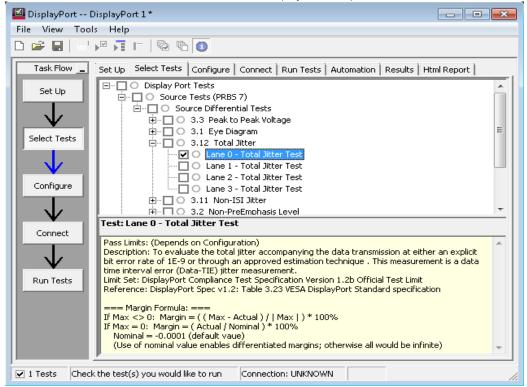

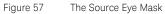

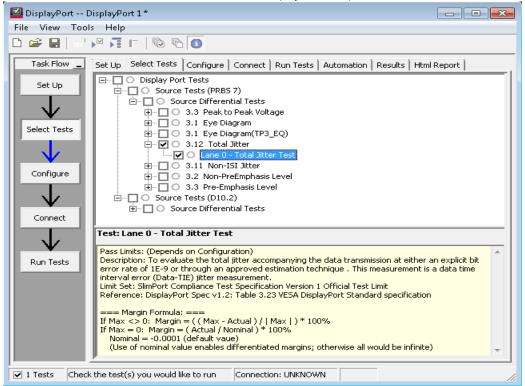

#### Source Total Jitter Test 71

Test ID71Test Overview71Test Conditions for Total Jitter Test71Test Setup72Measurement Procedure75PASS Condition75Test References75Expected/Observable Results75

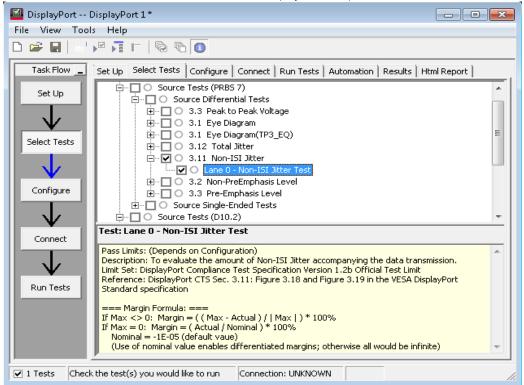

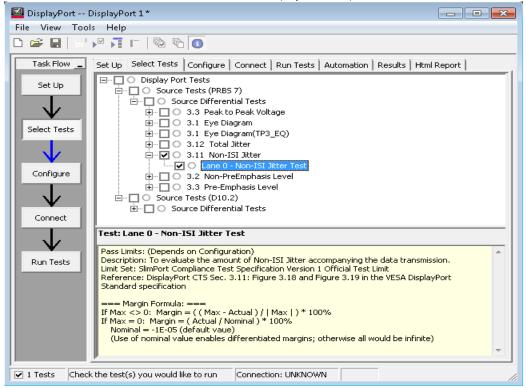

#### Source Non ISI Jitter Test 76

Test ID 76 Test Overview 76 Test Conditions for Non ISI Jitter Test 76 Test Setup 77 Measurement Procedure 80 PASS Condition 80 Test References 80 Expected/Observable Results 80

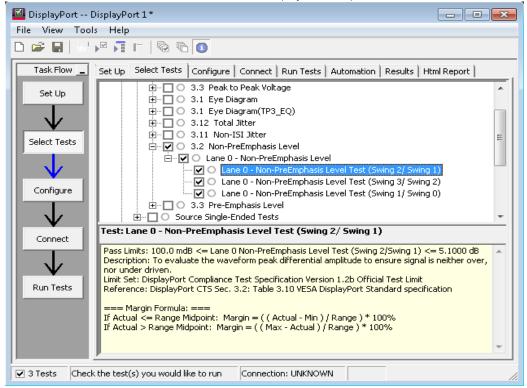

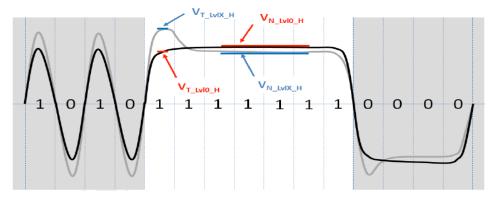

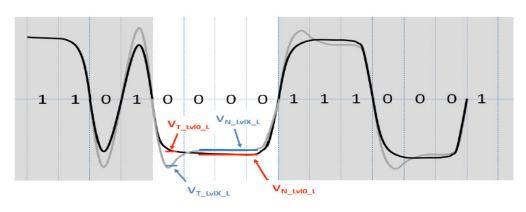

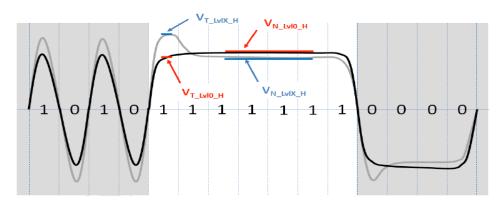

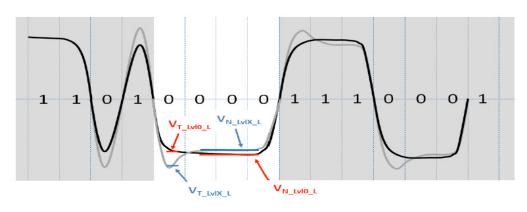

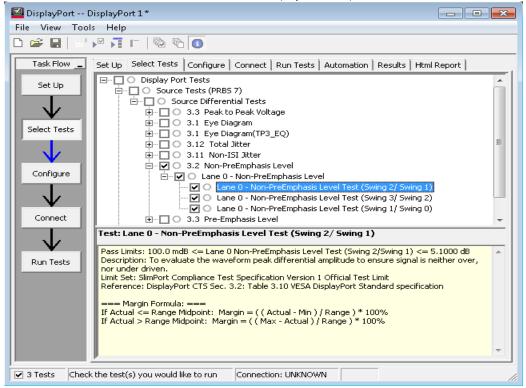

#### Source Non Pre-Emphasis Level Test 81

Test ID 81 Test Overview 81 Test Conditions for Non Pre-Emphasis Level Test 81 Test Setup 82 Measurement Procedure 85 PASS Condition 87 Test References 88 Expected/Observable Results 88

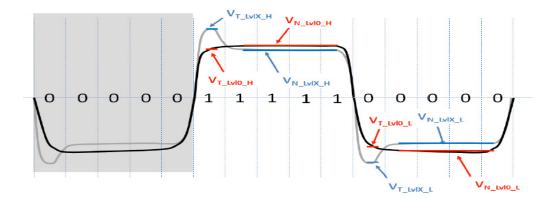

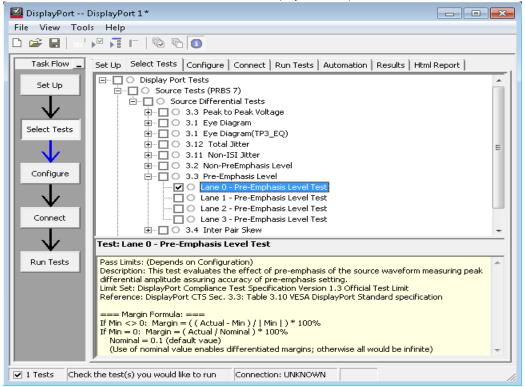

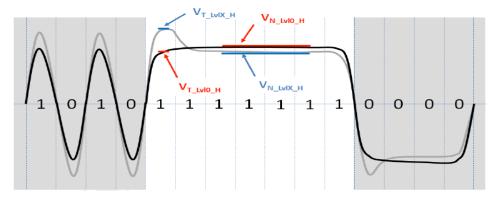

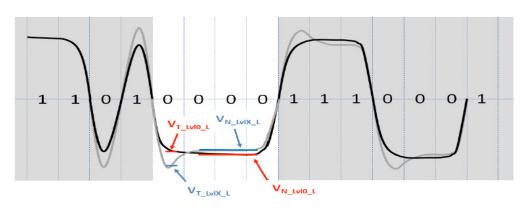

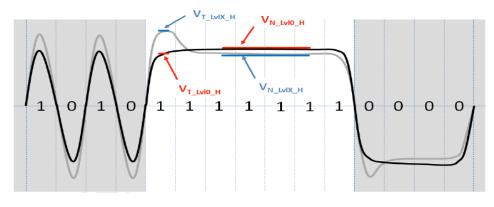

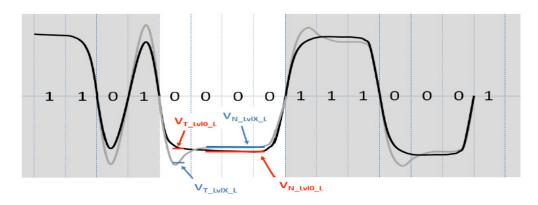

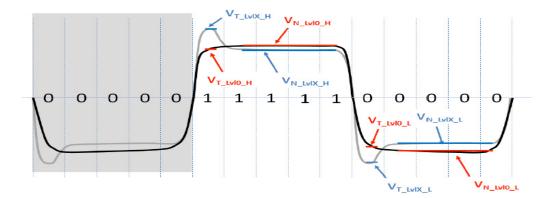

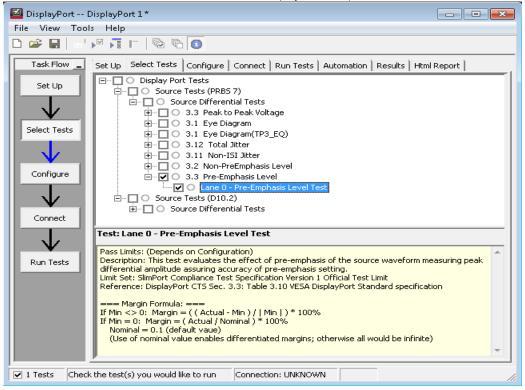

#### Source Pre-Emphasis Level Test 89

Test ID 89 Test Overview 89 Test Conditions for Pre-Emphasis Level Test 89 Test Setup 90 Measurement Procedure 93 PASS Condition 95 Test References 96 Expected/Observable Results 96

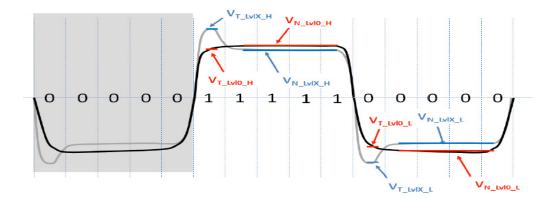

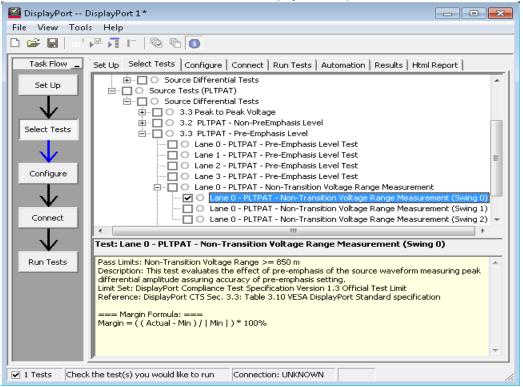

#### Source Non Transition Voltage Range Measurement Test 97

Test ID 97 Test Overview 97 Test Conditions for Non Transition Voltage Range Measurement Test 97 Test Setup 98 Measurement Procedure 101 PASS Condition 103 Test References 103 Expected/Observable Results 103

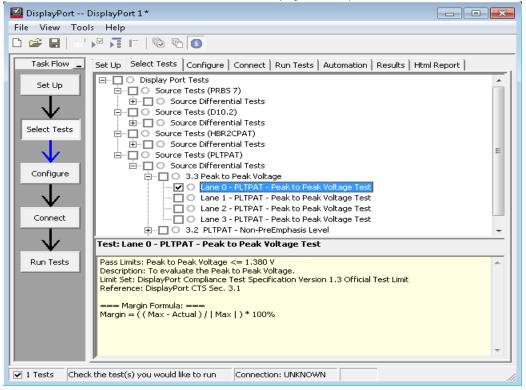

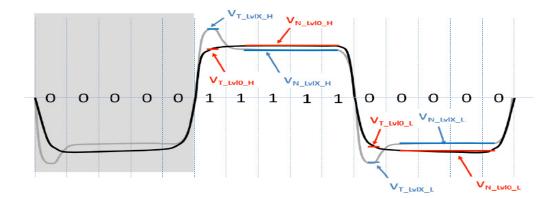

## Source Peak to Peak Voltage Test 104

Test ID 104 Test Overview 104 Test Conditions for Peak to Peak Voltage Test 104 Test Setup 105 Measurement Procedure 108 PASS Condition 108 Test References 108 Expected/Observable Results 108

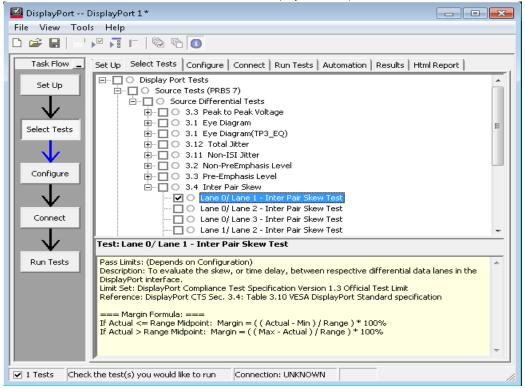

#### Source Inter Pair Skew Test 109

Test ID 109 Test Overview 109 Test Conditions for Inter Pair Skew Test 109 Test Setup 110 Measurement Procedure 113 PASS Condition 113 Test References 114 Expected/Observable Results 114

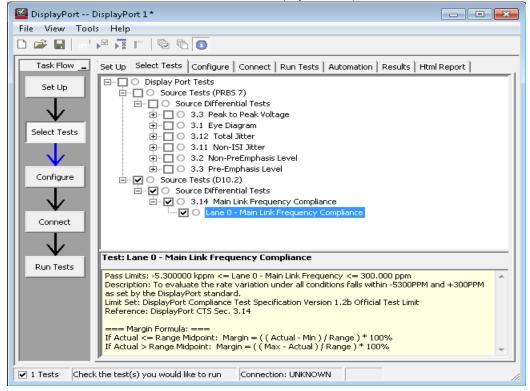

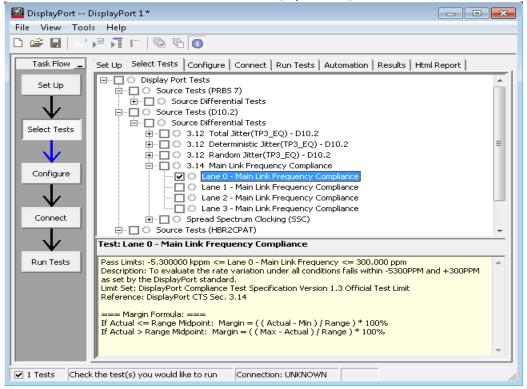

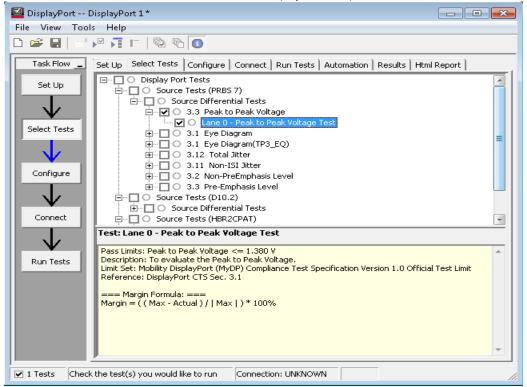

#### Source Main Link Frequency Compliance Test 115

Test ID 115 Test Overview 115 Test Conditions for Main Link Frequency Compliance Test 115 Test Setup 116 Measurement Procedure 119 PASS Condition 120 Test References 120 Expected/Observable Results 120

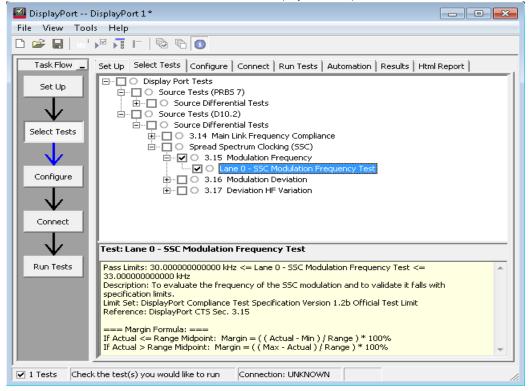

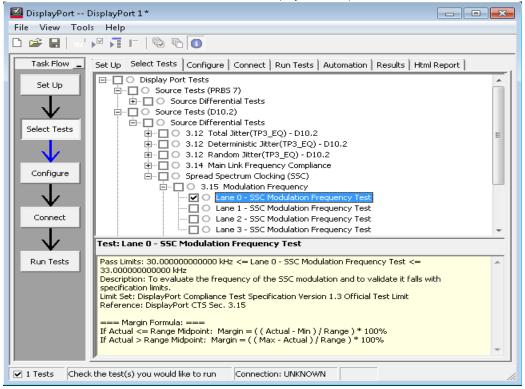

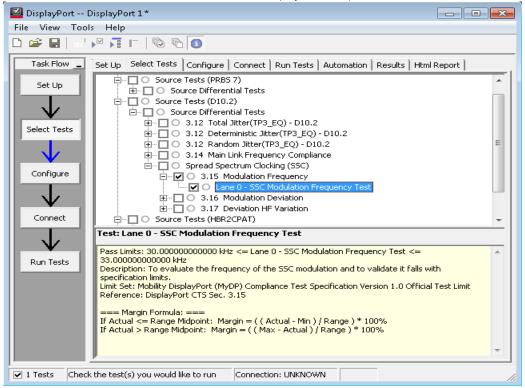

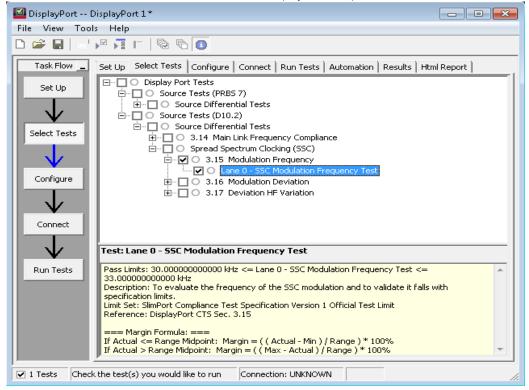

## Spread Spectrum Clocking (SSC) Modulation Frequency Test 121

Test ID 121 Test Overview 121 Test Conditions for SSC Modulation Frequency Test 121 Test Setup 122 Measurement Procedure 125 PASS Condition 125 Test References 126 Expected/Observable Results 126

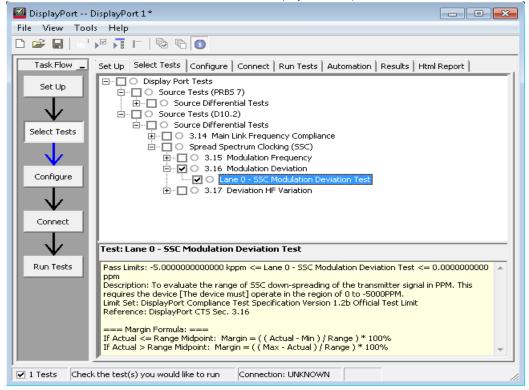

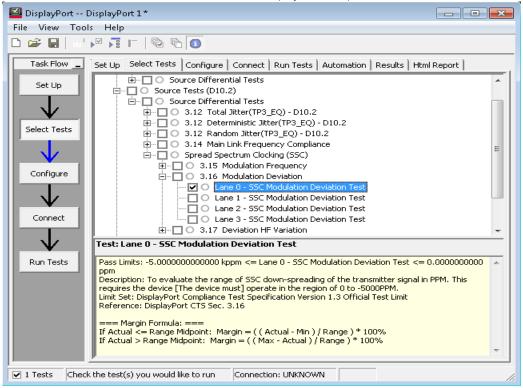

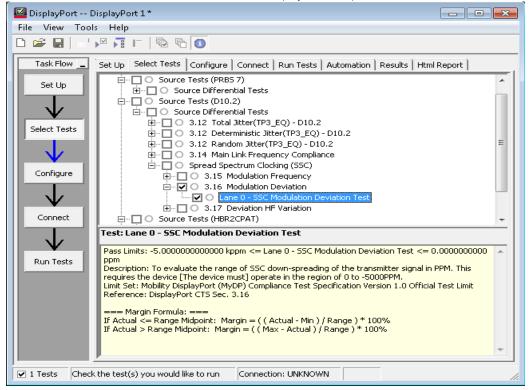

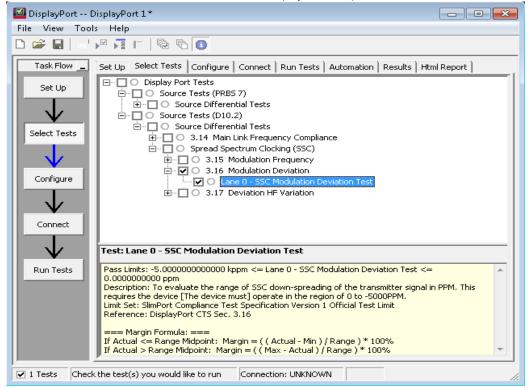

## Spread Spectrum Clocking (SSC) Modulation Deviation Test 127

Test ID 127 Test Overview 127 Test Conditions for SSC Modulation Deviation Test 127 Test Setup 128 Measurement Procedure 131 PASS Condition 132 Test References 132 Expected/Observable Results 132

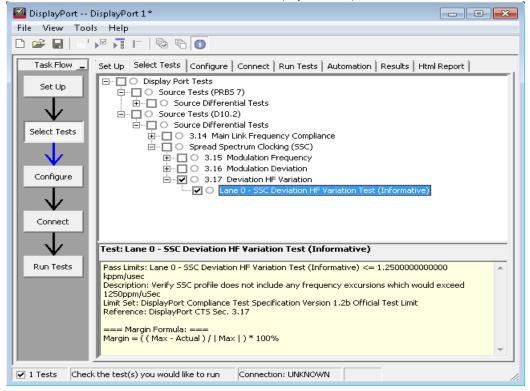

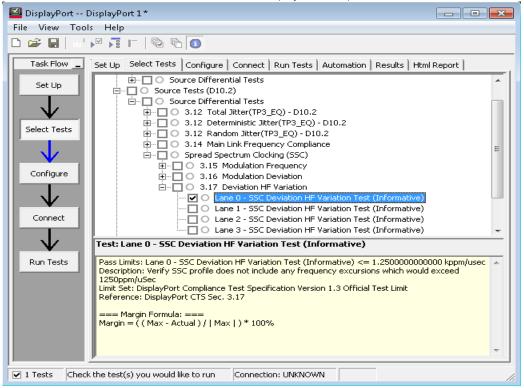

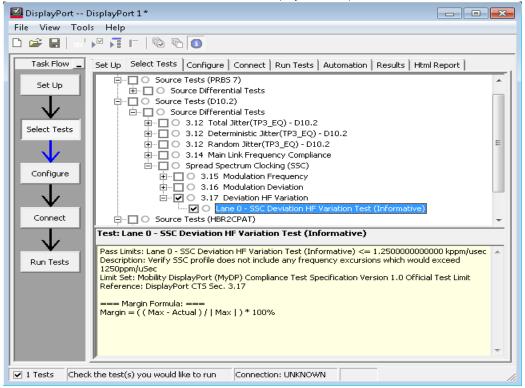

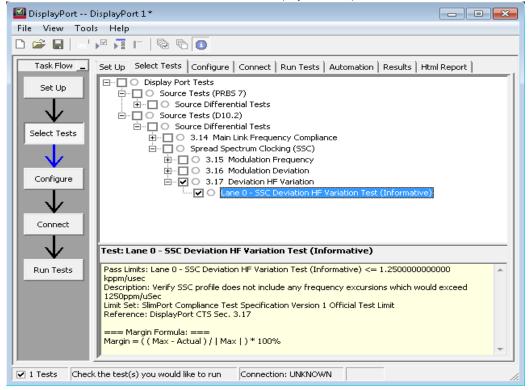

#### Spread Spectrum Clocking (SSC) Deviation HF Variation Test (Informative) 133

Test ID 133 Test Overview 133 Test Conditions for SSC Deviation HF Variation Test 133 Test Setup 134 Measurement Procedure 137 PASS Condition 137 Test References 138 Expected/Observable Results 138

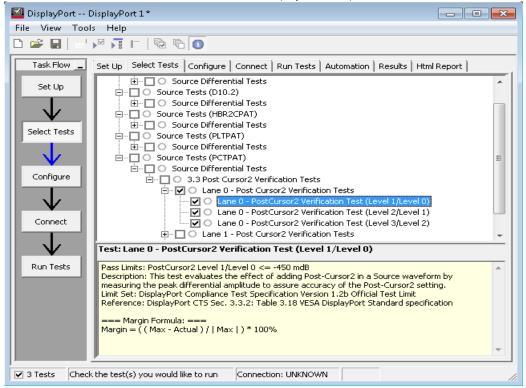

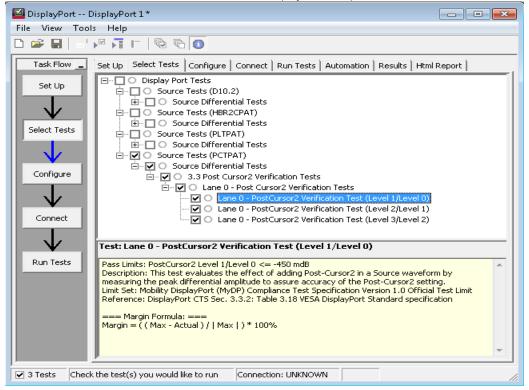

#### Source Post-Cursor 2 Verification Test (Informative) 139

Test ID 139 Test Overview 139 Test Conditions for Post Cursor 2 Verification Test 139 Test Setup 140 Measurement Procedure 143 PASS Condition 144 Test References 144 Expected/Observable Results 144

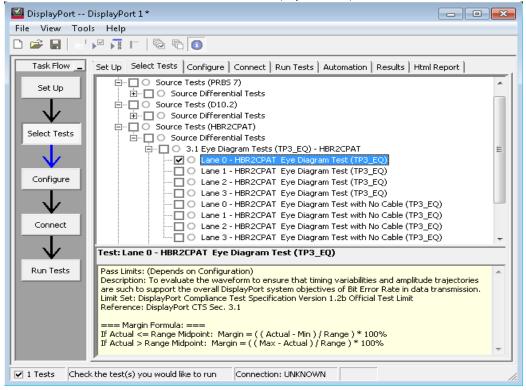

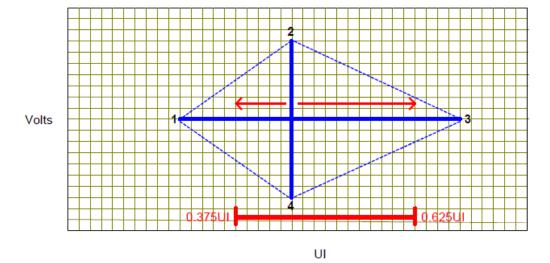

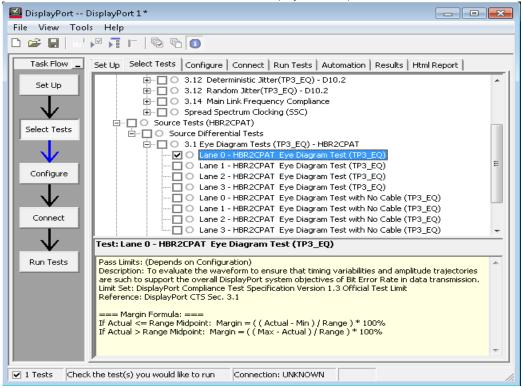

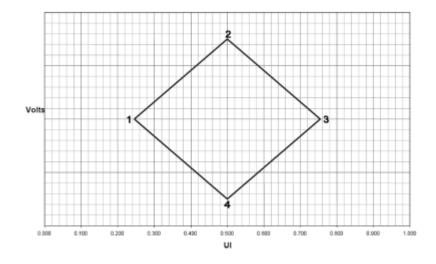

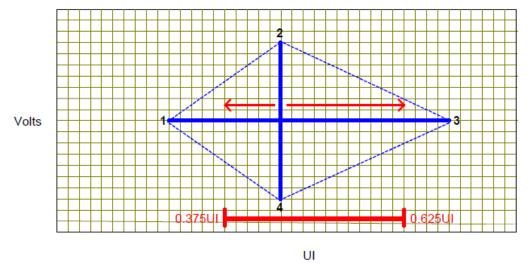

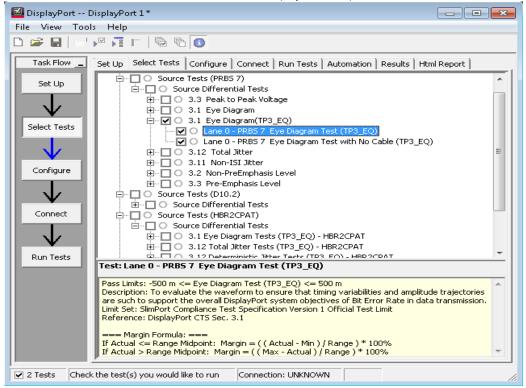

## Source Eye Diagram Test (TP3\_EQ) 145

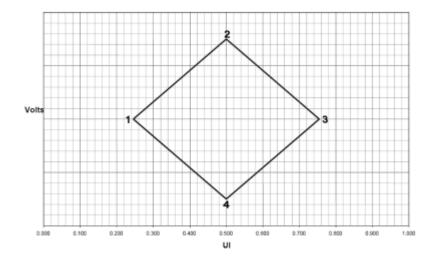

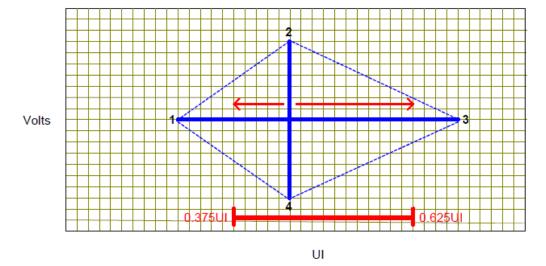

Test ID 145 Test Overview 145 Test Conditions for Eye Diagram Test (TP3\_EQ) 145 Test Setup 146 Measurement Procedure for HBR 149 Measurement Procedure for HBR2 149 PASS Condition 151 Test References 153 Expected/Observable Results 153

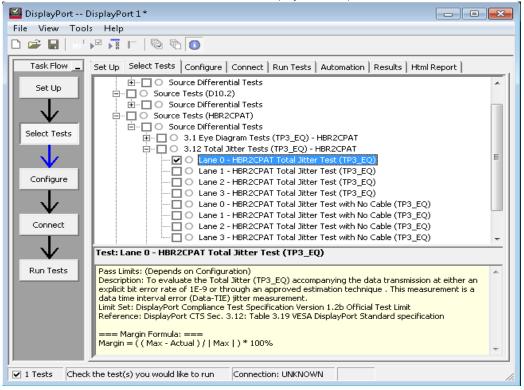

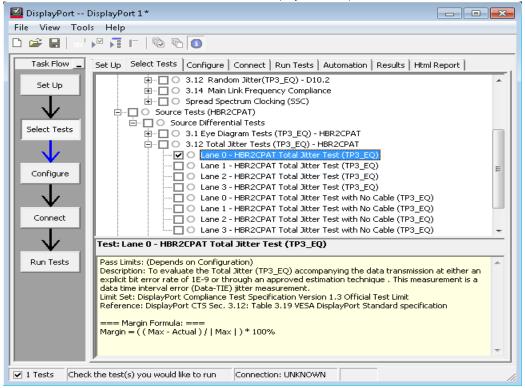

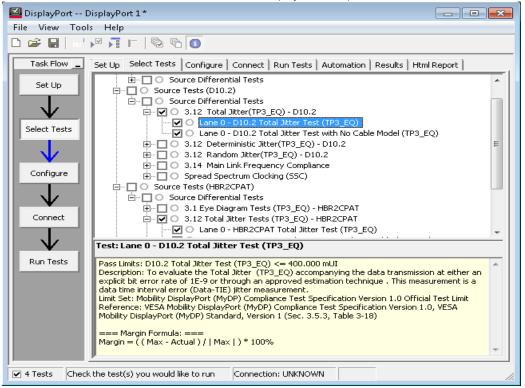

#### Source Total Jitter Test (TP3\_EQ) 154

Test ID 154 Test Overview 154 Test Conditions for Total Jitter Test (TP3\_EQ) 154 Test Setup 155 Measurement Procedure 158 PASS Condition 158 Test References 159 Expected/Observable Results 159

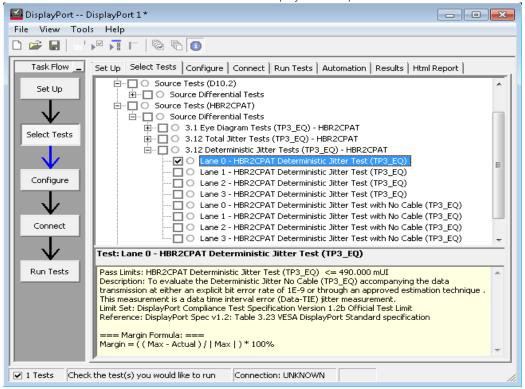

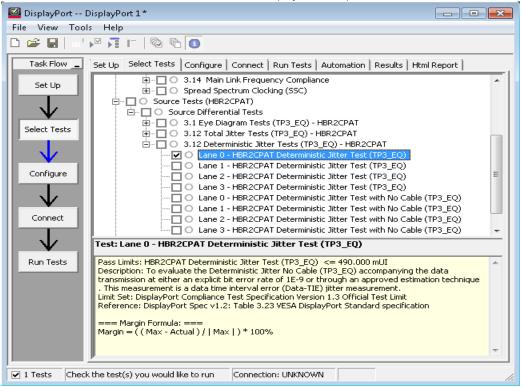

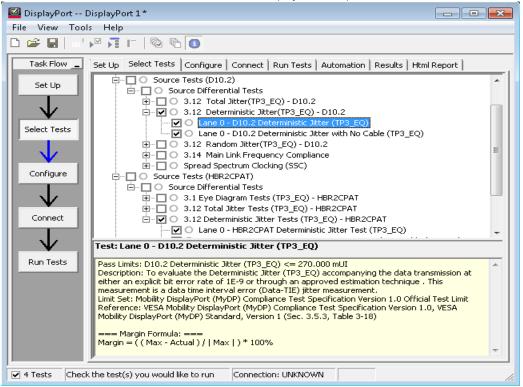

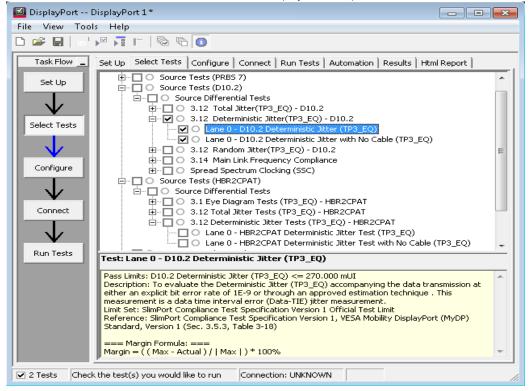

## Source Deterministic Jitter Test (TP3\_EQ) 160

Test ID 160 Test Overview 160 Test Conditions for Deterministic Jitter Test (TP3\_EQ) 160 Test Setup 161 Measurement Procedure 164 PASS Condition 164 Test References 165 Expected/Observable Results 165

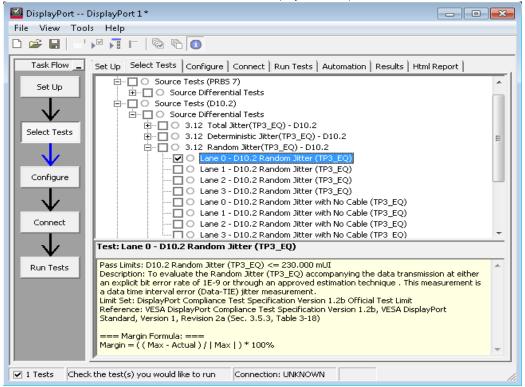

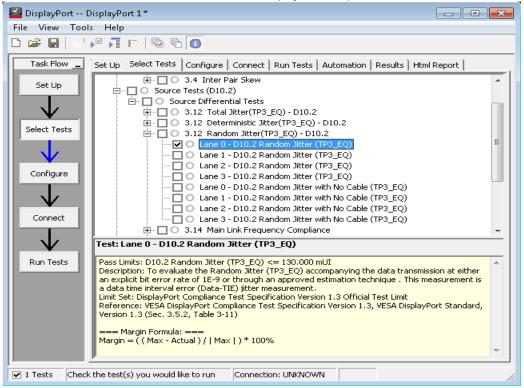

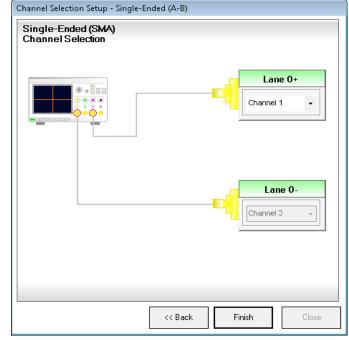

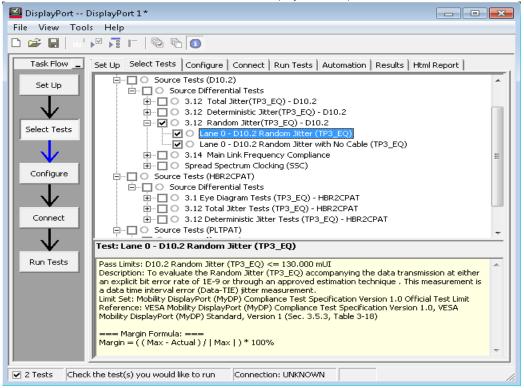

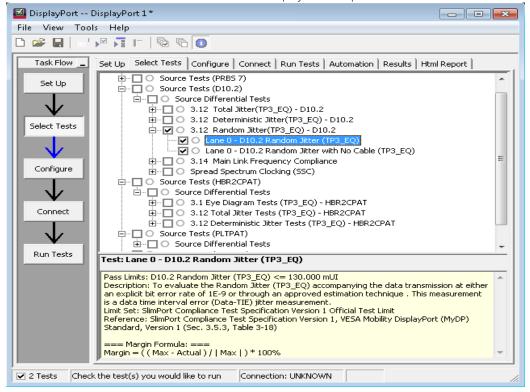

#### Source Random Jitter Test (TP3\_EQ) 166

Test ID 166 Test Overview 166 Test Conditions for Random Jitter Test (TP3\_EQ) 166 Test Setup 167 Measurement Procedure 170 PASS Condition 170 Test References 170 Expected/Observable Results 170

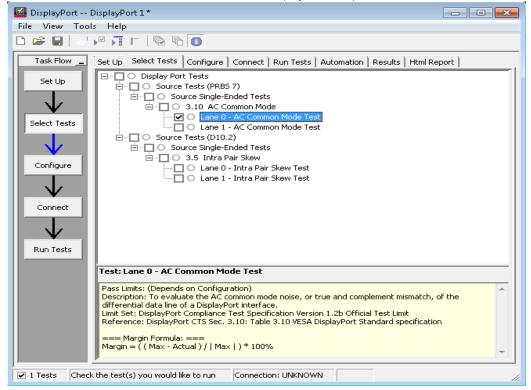

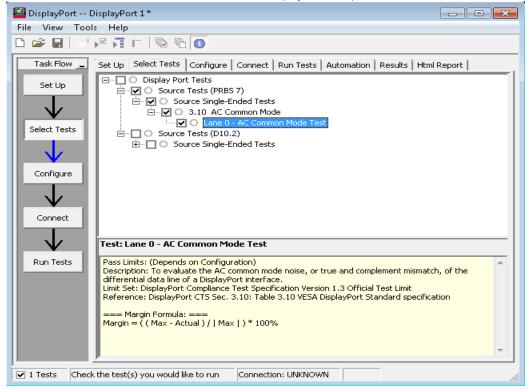

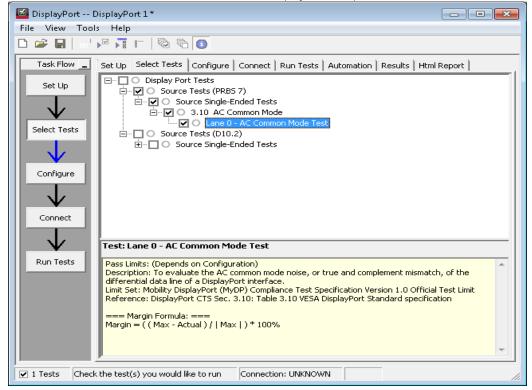

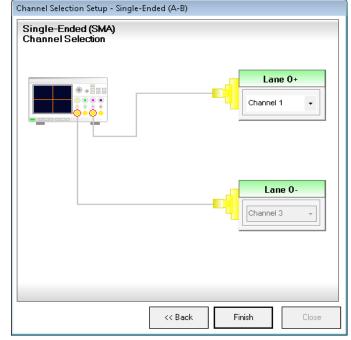

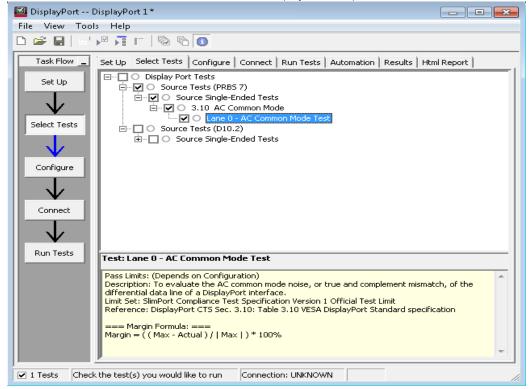

#### Source AC Common Mode Test (Informative) 171

Test ID 171 Test Overview 171 Test Conditions for AC Common Mode Test (Informative) 171 Test Setup 172 Measurement Procedure 175 PASS Condition 175 Test References 175 Expected/Observable Results 175

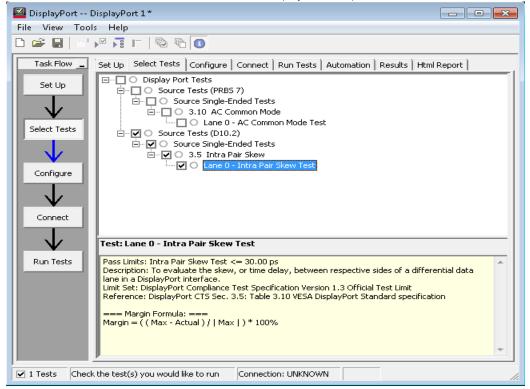

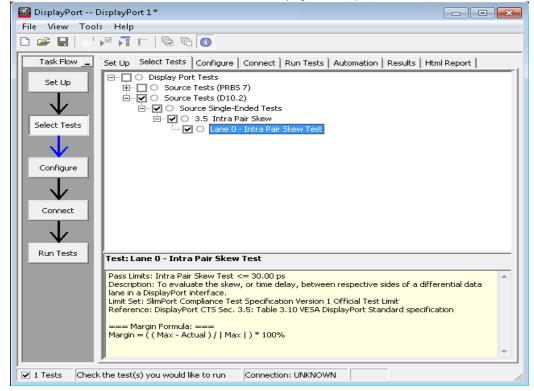

## Source Intra-Pair Skew Test (Informative) 176

Test ID 176 Test Overview 176 Test Conditions for Intra-Pair Skew Test (Informative) 176 Test Setup 177 Measurement Procedure 180 PASS Condition 180 Test References 180 Expected/Observable Results 181

## 4 DisplayPort 1.2 Sink Tests

#### **Overview** 184

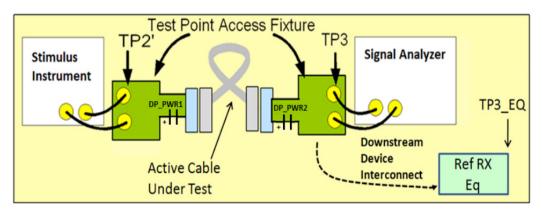

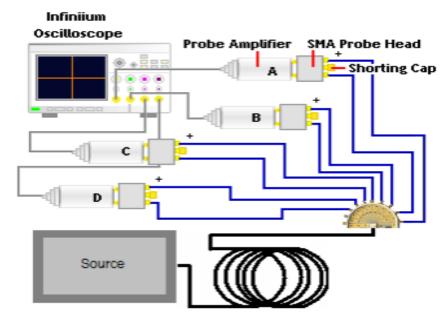

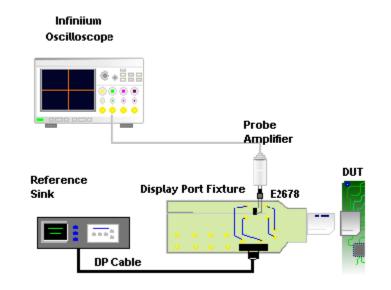

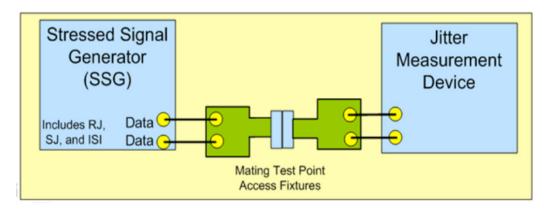

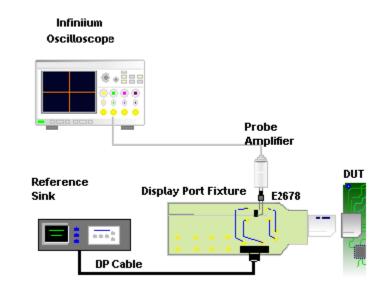

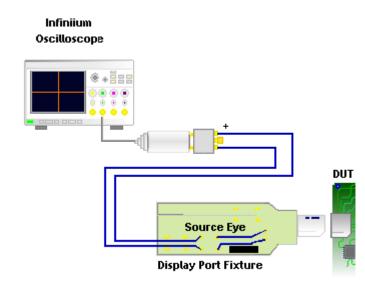

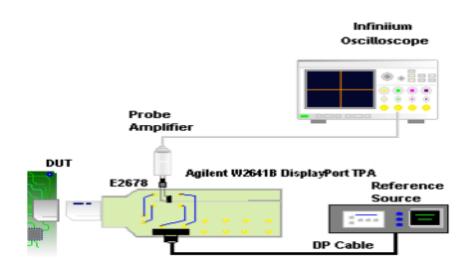

Test Point Definition for DisplayPort 1.2 (1.2b) Sink Tests184Calibration of Stress Signal185Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.2 Sink Tests186Probing/Connection Set Up for DisplayPort 1.2 Sink Tests188

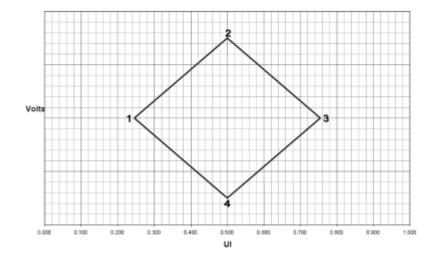

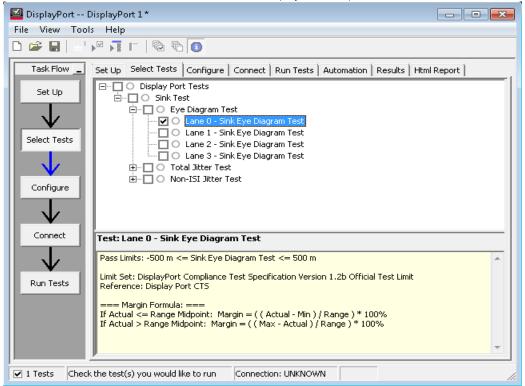

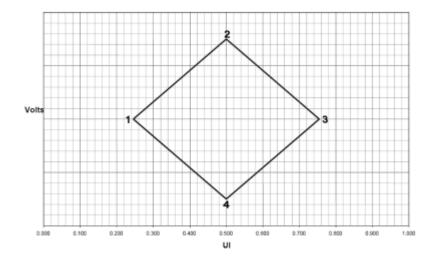

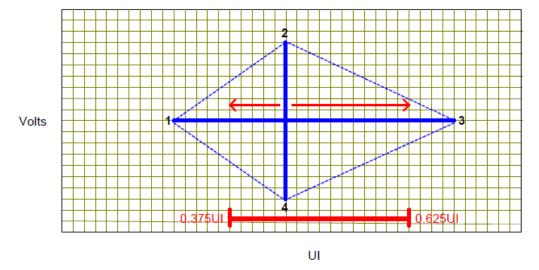

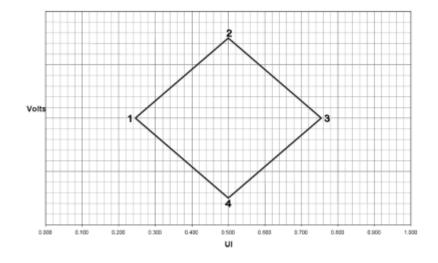

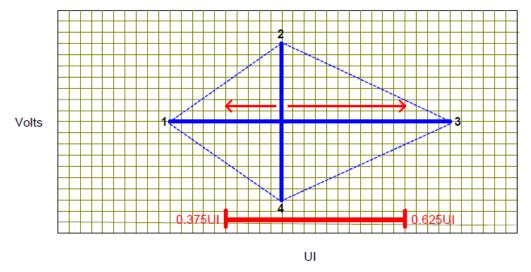

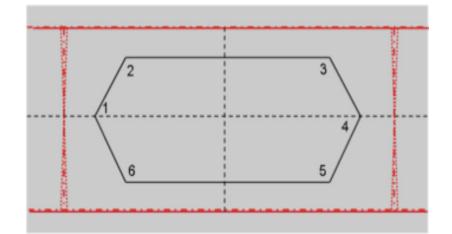

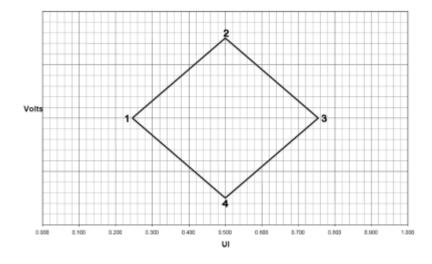

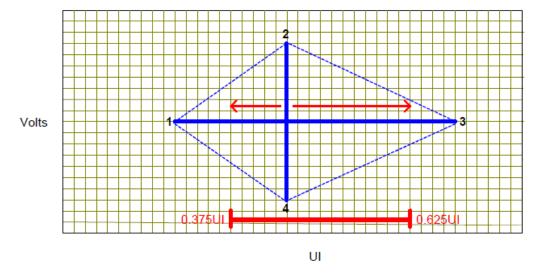

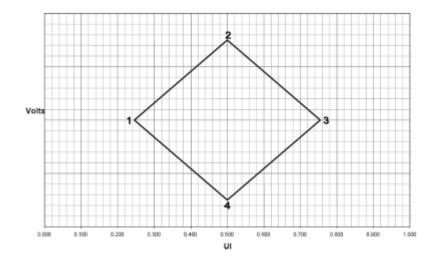

## Sink Eye Diagram Test 189

Test ID 189 Test Overview 189 Test Conditions for Eye Diagram Test 189 Test Setup 190 Measurement Procedure 193 PASS Condition 193 Test References 195 Expected/Observable Results 195

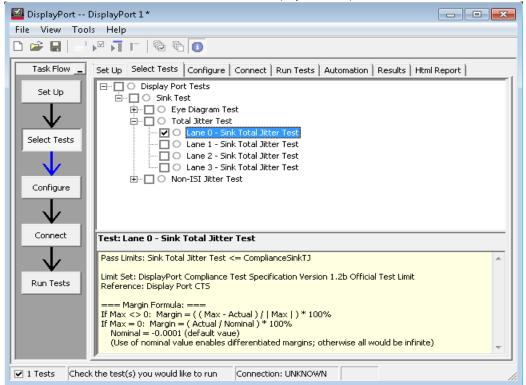

## Sink Total Jitter Test 196

Test ID 196 Test Overview 196 Test Conditions for Total Jitter Test 196 Test Setup 197 Measurement Procedure 200 PASS Condition 200 Test References 201 Expected/Observable Results 201

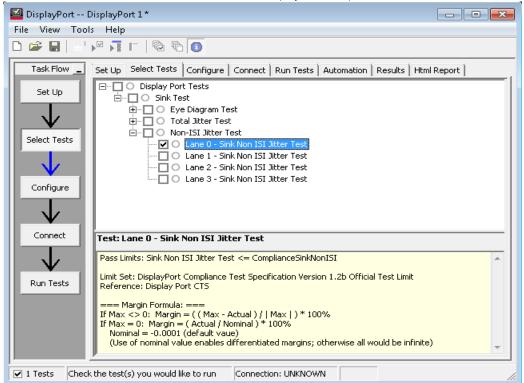

## Sink Non-ISI Jitter Test 202

Test ID202Test Overview202Test Conditions for Non-ISI Jitter Test202Test Setup203Measurement Procedure206PASS Condition206Test References207Expected/Observable Results207

## 5 DisplayPort 1.2 Cable Tests

#### **Overview** 210

Test Point Definition for DisplayPort 1.2 (1.2b) Cable Tests210Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.2 Cable Tests212Probing/Connection Set Up for DisplayPort 1.2 Cable Tests213

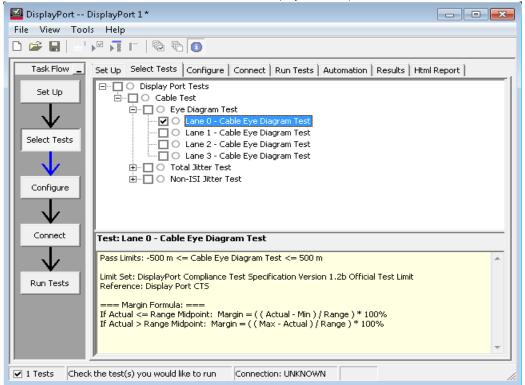

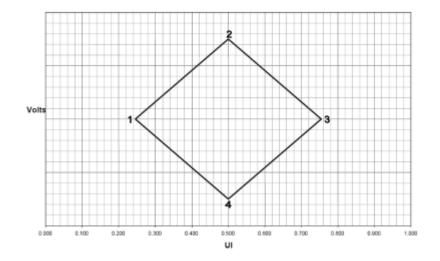

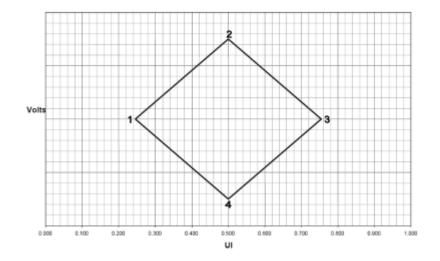

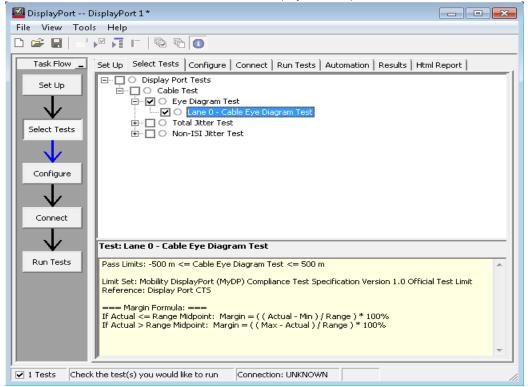

#### Cable Eye Diagram Test 214

Test ID 214 Test Overview 214 Test Conditions for Cable Eye Diagram Test 214 Test Setup 215 Measurement Procedure 218 PASS Condition 218 Test References 219 Expected/Observable Results 219

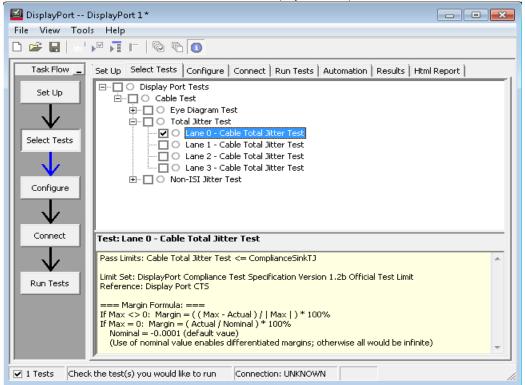

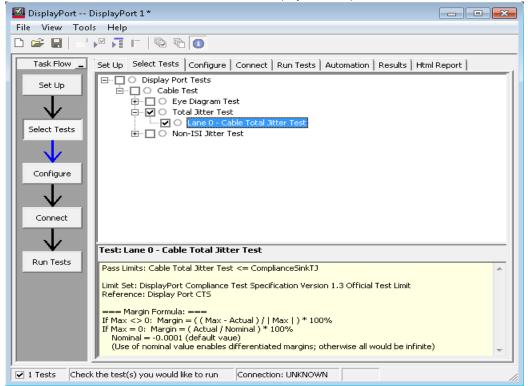

#### Cable Total Jitter Test 220

Test ID220Test Overview220Test Conditions for Cable Total Jitter Test220Test Setup221Measurement Procedure224PASS Condition224Test References224Expected/Observable Results224

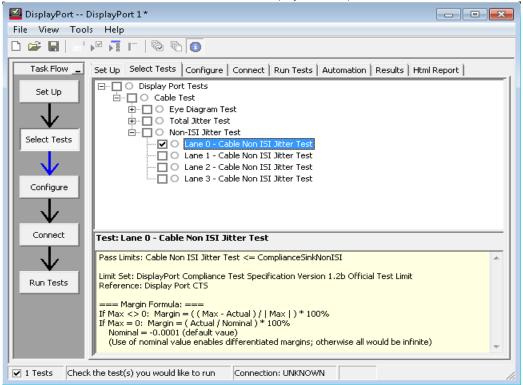

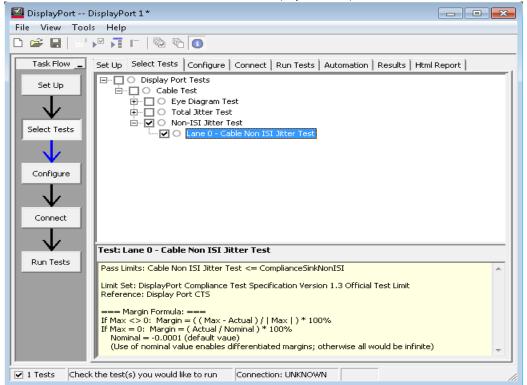

#### Cable Non-ISI Jitter Test 225

Test ID 225 Test Overview 225 Test Conditions for Cable Non-ISI Jitter Test 225 Test Setup 226 Measurement Procedure 229 PASS Condition 229 Test References 229 Expected/Observable Results 229

#### 6 DisplayPort 1.2 AUX Channel Tests

#### **Overview** 232

Test Point for AUX Channel Tests232Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.2 AUX ChannelTests232

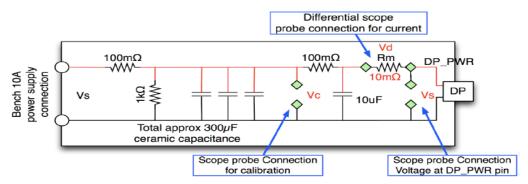

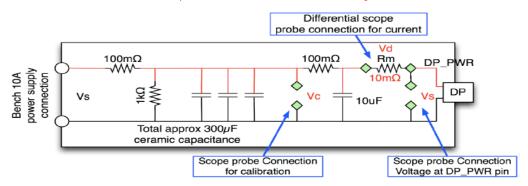

## Setting Up for AUX PHY and Inrush Tests 235

Probing/Connection Set Up for AUX Channel Tests 241

#### AUX Channel Unit Interval Test 243

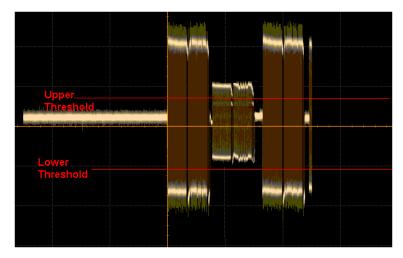

Test ID 243 Test Overview 243 Test Conditions 243 Measurement Procedure 243 PASS Condition 244 Test References 244 Expected/Observable Results 244

## AUX Channel Eye Test 245

Test ID 245 Test Overview 245 Test Conditions 245 Measurement Procedure 245 PASS Condition 246 Test References 246 Expected/Observable Results 246

## AUX Channel Peak-to-Peak Voltage Test 247

Test ID 247 Test Overview 247 Test Conditions 247 Measurement Procedure 247 PASS Condition 248 Test References 248 Expected/Observable Results 248

## AUX Channel Eye Sensitivity Calibration Test 249

Test ID249Test Overview249Test Conditions249Measurement Procedure249PASS Condition250Test References250Expected/Observable Results250

#### AUX Channel Eye Sensitivity Test 251

Test ID 251 Test Overview 251 Test Conditions 251 Measurement Procedure 251 PASS Condition 251 Test References 252 Expected/Observable Results 252

## 7 DisplayPort 1.2 Inrush Tests

#### **Overview** 254

Test Point for Inrush Tests254Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.2 Inrush Tests255

#### Inrush Energy Power Test 257

Test ID 257 Test Overview 257 Test Conditions 257 Measurement Procedure 257 PASS Condition 257 Test References 258 Expected/Observable Results 258

#### Inrush Peak Current Test 259

Test ID259Test Overview259Test Conditions259Measurement Procedure259PASS Condition259Test References260Expected/Observable Results260

## 8 DisplayPort 1.2 Dual Mode Tests

#### **Overview** 262

Test Point262Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.2 Dual Mode Tests262

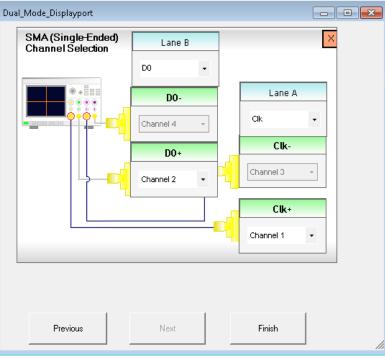

#### Setting Up for Dual Mode Tests 265

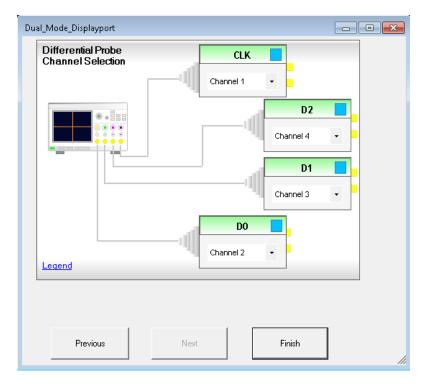

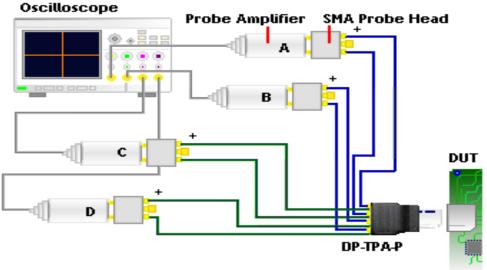

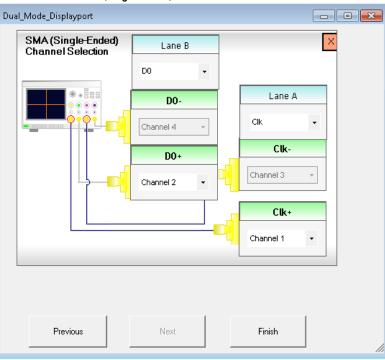

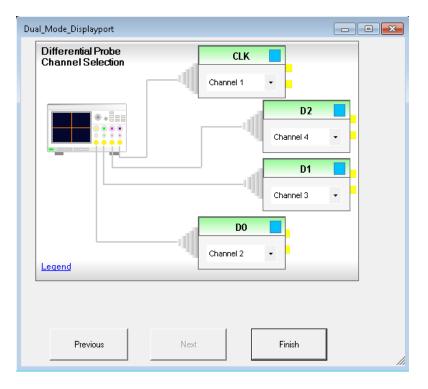

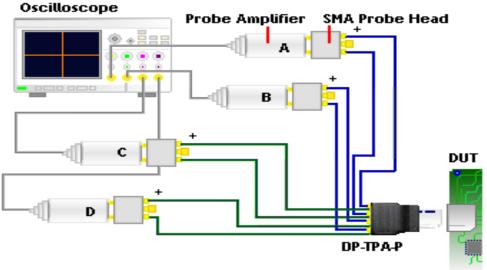

Probing/Connection Set Up for Dual Mode Tests 268

#### Dual Mode TMDS Clock Duty Cycle Test 269

Test ID269Test Overview269Test Conditions269Measurement Procedure269PASS Condition269Test References270Expected/Observable Results270

#### Dual Mode TMDS Clock Jitter Test 271

Test ID 271 Test Overview 271 Test Conditions 271 Measurement Procedure 271 PASS Condition 271 Test References 272 Expected/Observable Results 272

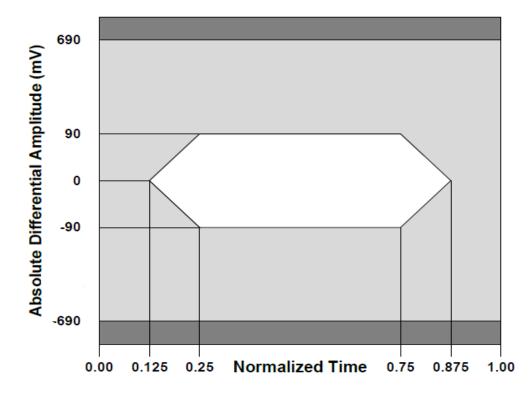

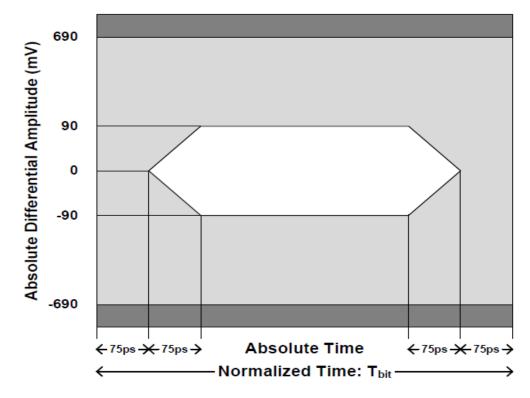

## Dual Mode Eye Diagram Test 273

Test ID 273 Test Overview 273 Test Conditions 273 Measurement Procedure 273 PASS Condition 274 Test References 275 Expected/Observable Results 275

## Dual Mode Data Jitter Test 276

Test ID276Test Overview276Test Conditions276Measurement Procedure276PASS Condition277Test References277Expected/Observable Results277

### Dual Mode Data Peak-Peak Differential Voltage Test 278

Test ID278Test Overview278Test Conditions278Measurement Procedure278PASS Condition279Test References279Expected/Observable Results279

#### Dual Mode Inter-Pair Skew Test 280

Test ID280Test Overview280Test Conditions280Measurement Procedure280PASS Condition281Test References281Expected/Observable Results281

#### Dual Mode Intra-Pair Skew Test 282

Test ID282Test Overview282Test Conditions282Measurement Procedure282PASS Condition283Test References283Expected/Observable Results283

## 9 DisplayPort 1.3 Source Tests

#### Overview 286

Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.3 Source Tests 291 Probing/Connection Set Up for DisplayPort 1.3 Source Tests 293

#### Source Eye Diagram Test 294

Test ID 294 Test Overview 294 Test Conditions for Eye Diagram Test 294 Test Setup 295 Measurement Procedure 298 PASS Condition 298 Test References 299 Expected/Observable Results 300

## Source Total Jitter Test 301

Test ID 301 Test Overview 301 Test Conditions for Total Jitter Test 301 Test Setup 302 Measurement Procedure 305 PASS Condition 305 Test References 305 Expected/Observable Results 305

#### Source Non-ISI Jitter Test 306

Test ID 306 Test Overview 306 Test Conditions for Non-ISI Jitter Test 306 Test Setup 307 Measurement Procedure 310 PASS Condition 310 Test References 310 Expected/Observable Results 310

#### Source Non Pre-Emphasis Level Test 311

Test ID 311 Test Overview 311 Test Conditions for Non Pre-Emphasis Level Test 311 Test Setup 312 Measurement Procedure 315 PASS Condition 317 Test References 318 Expected/Observable Results 318

#### Source Pre-Emphasis Level Test 319

Test ID 319 Test Overview 319 Test Conditions for Pre-Emphasis Level Test 320 Test Setup 320 Measurement Procedure 323 PASS Condition 325 Test References 326 Expected/Observable Results 326

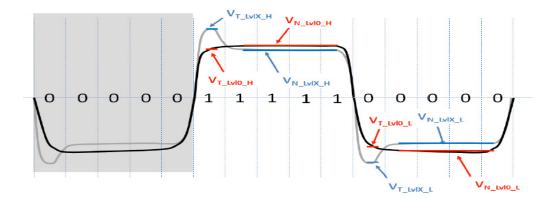

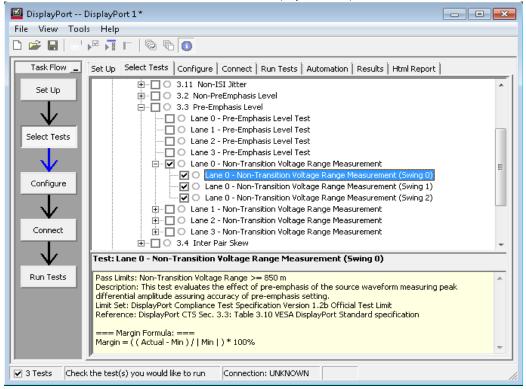

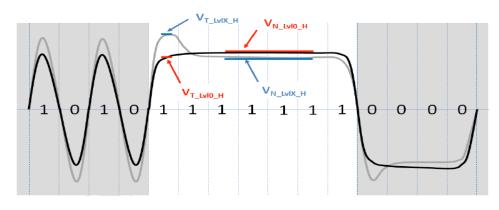

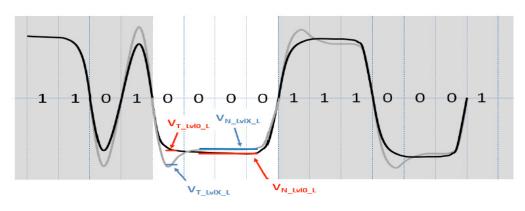

#### Source Non Transition Voltage Range Measurement Test 327

Test ID 327 Test Overview 327 Test Conditions for Non-Transition Voltage Range Measurement Test 327 Test Setup 328 Measurement Procedure 331 PASS Condition 333 Test References 333 Expected/Observable Results 333

## Source Peak to Peak Voltage Test 334

Test ID 334 Test Overview 334 Test Conditions for Peak to Peak Voltage Test 334 Test Setup 335 Measurement Procedure 338 PASS Condition 338 Test References 338 Expected/Observable Results 338

#### Source Inter-Pair Skew Test 339

Test ID 339 Test Overview 339 Test Conditions for Inter Pair Skew Test 339 Test Setup 340 Measurement Procedure 343 PASS Condition 343 Test References 344 Expected/Observable Results 344

## Source Main Link Frequency Compliance Test 345

Test ID 345 Test Overview 345 Test Conditions for Main Link Frequency Compliance Test 345 Test Setup 346 Measurement Procedure 349 PASS Condition 350 Test References 350 Expected/Observable Results 350

### Source Spread Spectrum Clocking (SSC) Modulation Frequency Test 351

Test ID 351 Test Overview 351 Test Conditions for SSC Modulation Frequency Test 351 Test Setup 352 Measurement Procedure 355 PASS Condition 355 Test References 356 Expected/Observable Results 356

## Source Spread Spectrum Clocking (SSC) Modulation Deviation Test 357

Test ID 357 Test Overview 357 Test Conditions for SSC Modulation Deviation Test 357 Test Setup 358 Measurement Procedure 361 PASS Condition 362 Test References 362 Expected/Observable Results 362

#### Source Spread Spectrum Clocking (SSC) Deviation HF Variation Test (Informative) 363

Test ID 363 Test Overview 363 Test Conditions for SSC Deviation HF Variation Test (Informative) 363 Test Setup 364 Measurement Procedure 367 PASS Condition 367 Test References 368 Expected/Observable Results 368

#### Source Eye Diagram Test (TP3\_EQ) 369

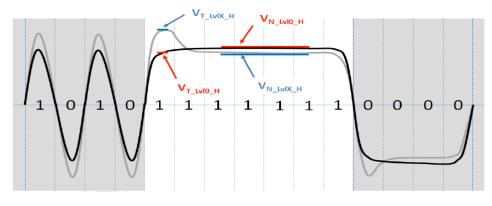

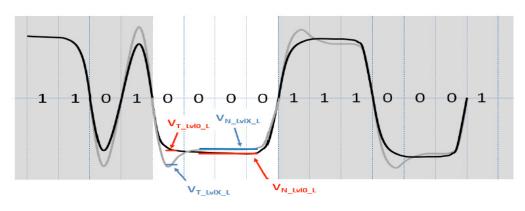

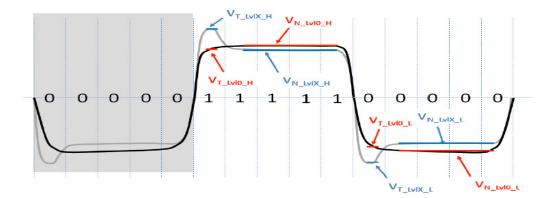

369 Test ID Test Overview 369 Test Conditions for Eye Diagram Test (TP3 EQ) 369 Test Setup 370 Measurement Procedure for HBR 373 Measurement Procedure for HBR2 and HBR3 373 375 PASS Condition Test References 377 Expected/Observable Results 378

## Source Total Jitter Test (TP3\_EQ) 379

Test ID 379 Test Overview 379 Test Conditions for Total Jitter Test (TP3\_EQ) 379 Test Setup 380 Measurement Procedure 383 PASS Condition 383 Test References 384 Expected/Observable Results 384

## Source Deterministic Jitter Test (TP3\_EQ) 385

Test ID 385 Test Overview 385 Test Conditions for Deterministic Jitter Test (TP3\_EQ) 385 Test Setup 386 Measurement Procedure 389 PASS Condition 389 Test References 390 Expected/Observable Results 390

#### Source Random Jitter Test (TP3\_EQ) 391

Test ID 391 Test Overview 391 Test Conditions for Random Jitter Test (TP3\_EQ) 391 Test Setup 392 Measurement Procedure 395 PASS Condition 395 Test References 395 Expected/Observable Results 395

#### Source AC Common Mode Test (Informative) 396

Test ID 396 Test Overview 396 Test Conditions for AC Common Mode Test (Informative) 396 Test Setup 397 Measurement Procedure 400 PASS Condition 400 Test References 400 Expected/Observable Results 400

#### Source Intra-Pair Skew Test (Informative) 401

Test ID 401 Test Overview 401 Test Conditions for Intra-Pair Skew Test (Informative) 401 Test Setup 402 Measurement Procedure 405 PASS Condition 405 Test References 405 Expected/Observable Results 406

#### 10 DisplayPort 1.3 Sink Tests

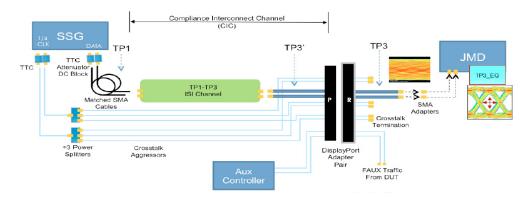

#### **Overview** 408

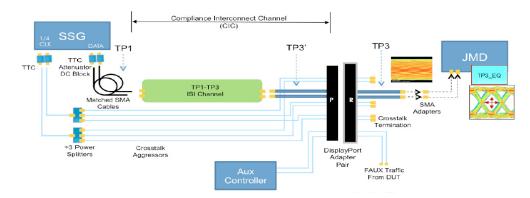

Test Point Definition for DisplayPort 1.3 Sink Tests408Calibration of Stress Signal409Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.3 Sink Tests410Probing/Connection Set Up for DisplayPort 1.3 Sink Tests412

## Sink Eye Diagram Test 413

Test ID 413 Test Overview 413 Test Conditions for Eye Diagram Test 413 Test Setup 414 Measurement Procedure 417 PASS Condition 417 Test References 419 Expected/Observable Results 420

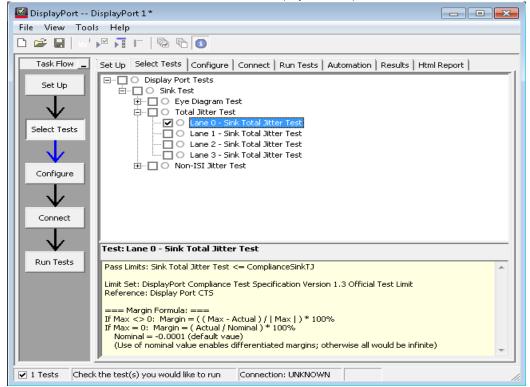

## Sink Total Jitter Test 421

Test ID 421 Test Overview 421 Test Conditions for Total Jitter Test 421 Test Setup 422 Measurement Procedure 425 PASS Condition 425 Test References 426 Expected/Observable Results 426

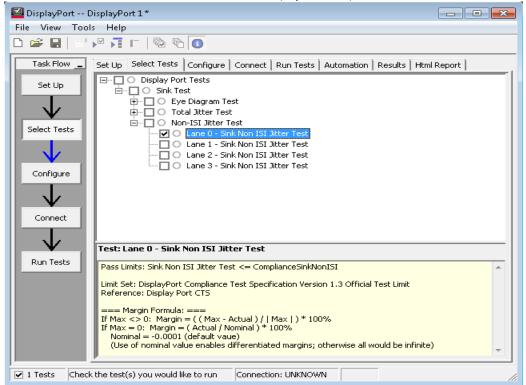

#### Sink Non-ISI Jitter Test 427

Test ID 427 Test Overview 427 Test Conditions for Sink Non-ISI Jitter Test 427 Test Setup 428 Measurement Procedure 431 PASS Condition 431 Test References 432 Expected/Observable Results 432

#### 11 DisplayPort 1.3 Cable Tests

#### **Overview** 434

Test Point Definition for DisplayPort 1.3 Cable Tests434Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.3 Cable Tests436Probing/Connection Set Up for DisplayPort 1.3 Cable Tests437

#### Cable Eye Diagram Test 438

Test ID 438 Test Overview 438 Test Conditions for Eye Diagram Test 438 Test Setup 439 Measurement Procedure 442 PASS Condition 442 Test References 443 Expected/Observable Results 443

#### Cable Total Jitter Test 444

Test ID 444 Test Overview 444 Test Conditions for Total Jitter Test 444 Test Setup 445 Measurement Procedure 448 PASS Condition 448 Test References 448 Expected/Observable Results 448

#### Cable Non-ISI Jitter Test 449

Test ID 449 Test Overview 449 Test Conditions for Non-ISI Jitter Test 449 Test Setup 450 Measurement Procedure 453 PASS Condition 453 Test References 453 Expected/Observable Results 453

## 12 DisplayPort 1.3 AUX Channel Tests

#### **Overview** 456

Test Point for AUX Channel Tests 456 Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.3 AUX Channel Tests 456

## Setting Up for AUX PHY and Inrush Tests 459

Probing/Connection Set Up for AUX Channel Tests 465

#### AUX Channel Unit Interval Test 467

Test ID 467 Test Overview 467 Test Conditions 467 Measurement Procedure 467 PASS Condition 468 Test References 468 Expected/Observable Results 468

#### AUX Channel Eye Test 469

Test ID 469 Test Overview 469 Test Conditions 469 Measurement Procedure 469 PASS Condition 470 Test References 470 Expected/Observable Results 470

## AUX Channel Peak-to-Peak Voltage Test 471

Test ID 471 Test Overview 471 Test Conditions 471 Measurement Procedure 471 PASS Condition 472 Test References 472 Expected/Observable Results 472

## AUX Channel Eye Sensitivity Calibration Test 473

Test ID 473 Test Overview 473 Test Conditions 473 Measurement Procedure 473 PASS Condition 474 Test References 474 Expected/Observable Results 474

## AUX Channel Eye Sensitivity Test 475

Test ID 475 Test Overview 475 Test Conditions 475 Measurement Procedure 475 PASS Condition 475 Test References 476 Expected/Observable Results 476

## 13 DisplayPort 1.3 Inrush Tests

#### **Overview** 478

Test Point478Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.3 Inrush Tests479

#### Inrush Energy Power Test 481

Test ID 481 Test Overview 481 Test Conditions 481 Measurement Procedure 481 PASS Condition 481 Test References 482 Expected/Observable Results 482

#### Inrush Peak Current Test 483

Test ID 483 Test Overview 483 Test Conditions 483 Measurement Procedure 483 PASS Condition 483 Test References 484 Expected/Observable Results 484

## 14 DisplayPort 1.3 Dual Mode Tests

#### **Overview** 486

Test Point 486 Setting Up the DisplayPort Compliance Test Application for DisplayPort 1.3 Dual Mode Tests 487

#### Setting Up for Dual Mode Tests 490

Probing/Connection Set Up for Dual Mode Tests 493

## Dual Mode TMDS Clock Duty Cycle Test 494

Test ID 494 Test Overview 494 Test Conditions 494 Measurement Procedure 494 PASS Condition 494 Test References 495 Expected/Observable Results 495

#### Dual Mode TMDS Clock Jitter Test 496

Test ID 496 Test Overview 496 Test Conditions 496 Measurement Procedure 496 PASS Condition 496 Test References 497 Expected/Observable Results 497

#### **Dual Mode Eye Diagram Test** 498

Test ID 498 Test Overview 498 Test Conditions 498 Measurement Procedure 498 PASS Condition 499 Test References 500 Expected/Observable Results 500

#### Dual Mode Data Jitter Test 501

Test ID501Test Overview501Test Conditions501Measurement Procedure501PASS Condition502Test References502Expected/Observable Results502

## Dual Mode Data Peak-Peak Differential Voltage Test 503

Test ID503Test Overview503Test Conditions503Measurement Procedure503PASS Condition504Test References504Expected/Observable Results504

#### Dual Mode Inter-Pair Skew Test 505

Test ID505Test Overview505Test Conditions505Measurement Procedure505PASS Condition506Test References506Expected/Observable Results506

#### Dual Mode Intra-Pair Skew Test 507

Test ID 507 Test Overview 507 Test Conditions 507 Measurement Procedure 507 PASS Condition 508 Test References 508 Expected/Observable Results 508

## 15 MyDP 1.0 Source Tests

#### **Overview** 510

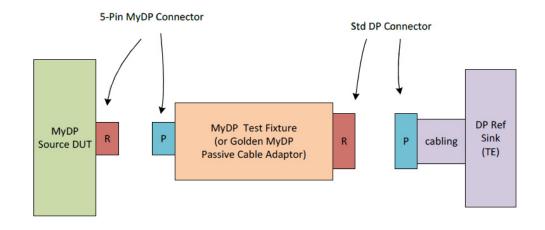

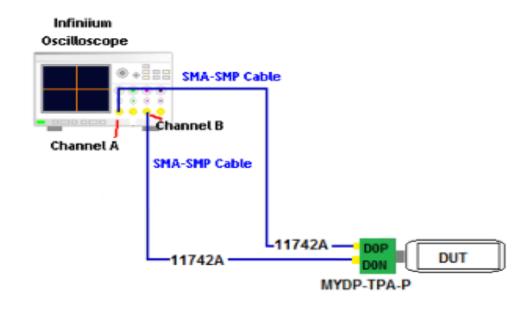

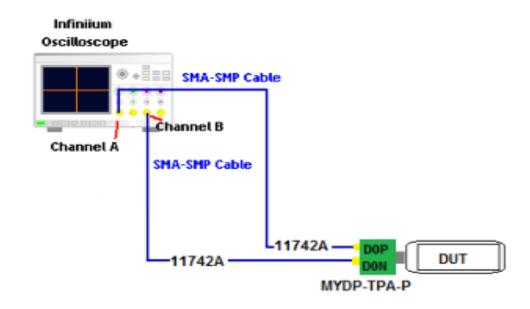

Test Point Definition for MyDP 1.0 Source Tests512Setting Up the DisplayPort Compliance Test Application for DisplayPort MyDP 1.0 SourceTests513Probing/Connection Set Up for MyDP 1.0 Source Tests515

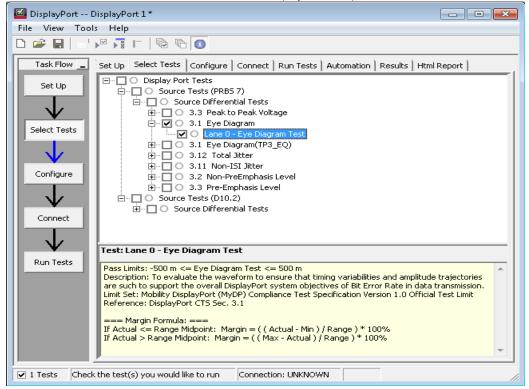

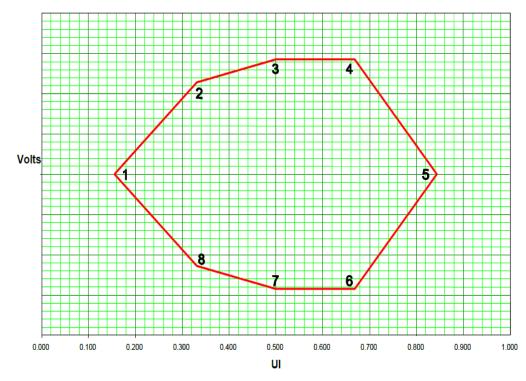

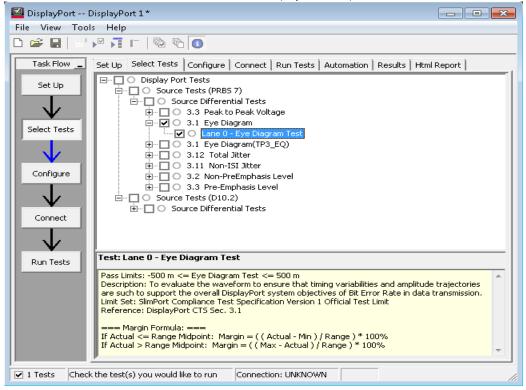

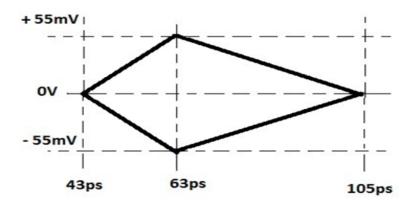

#### Source Eye Diagram Test 516

Test ID 516 Test Overview 516 Test Conditions for Eye Diagram Test 516 Test Setup 517 Measurement Procedure 520 PASS Condition 520 Test References 521 Expected/Observable Results 522

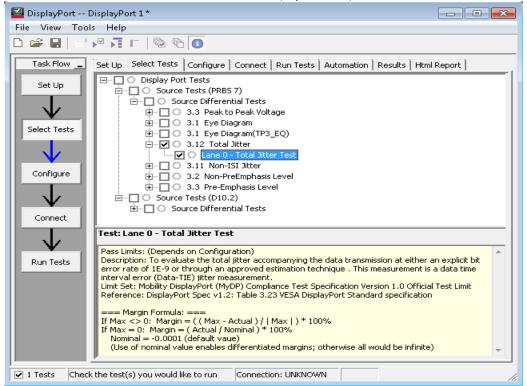

#### Source Total Jitter Test 523

Test ID 523 Test Overview 523 Test Conditions for Total Jitter Test 523 Test Setup 524 Measurement Procedure 527 PASS Condition 527 Test References 527 Expected/Observable Results 527

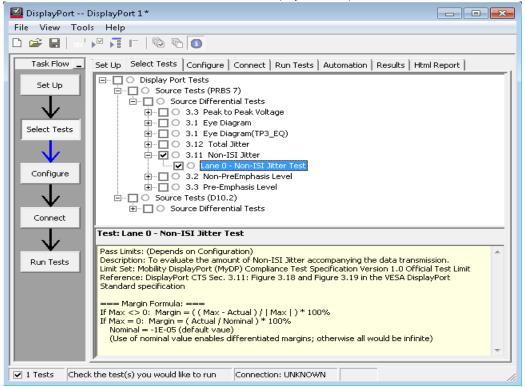

## Source Non-ISI Jitter Test 528

Test ID 528 Test Overview 528 Test Conditions for Non-ISI Jitter Test 528 Test Setup 529 Measurement Procedure 532 PASS Condition 532 Test References 532 Expected/Observable Results 532

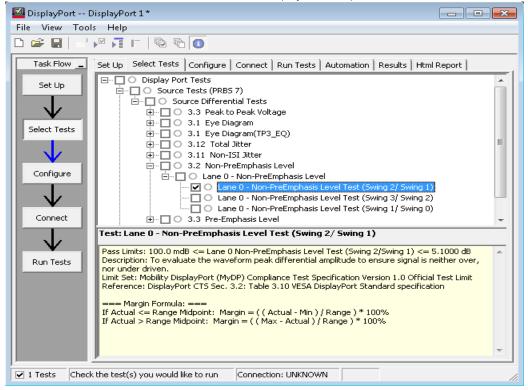

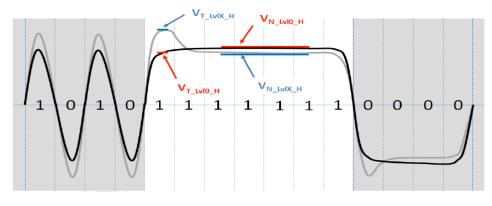

## Source Non Pre-Emphasis Level Test 533

Test ID 533 Test Overview 533 Test Conditions for Non Pre-Emphasis Level Test 533 Test Setup 534 Measurement Procedure 537 PASS Condition 539 Test References 540 Expected/Observable Results 540

#### Source Pre-Emphasis Level Differential Tests 541

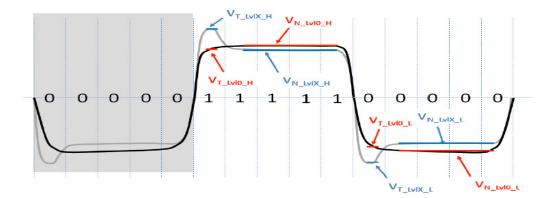

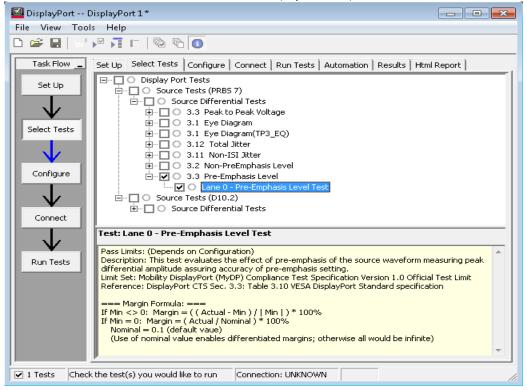

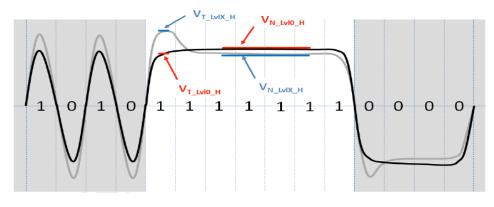

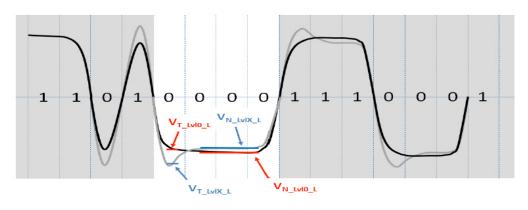

Test ID 541 Test Overview 541 Test Conditions for Pre-Emphasis Level Test 541 Test Setup 542 Measurement Procedure 545 PASS Condition 547 Test References 548 Expected/Observable Results 548

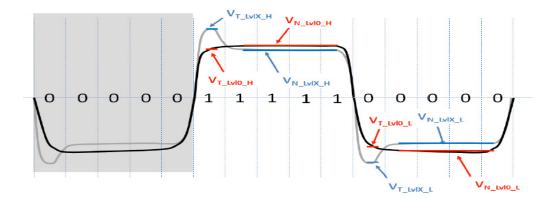

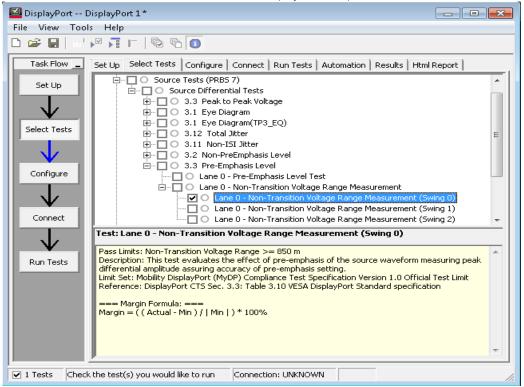

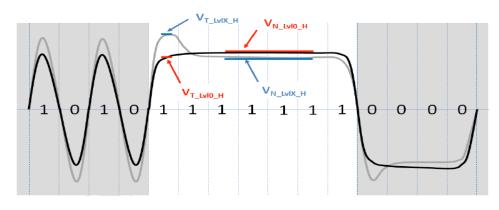

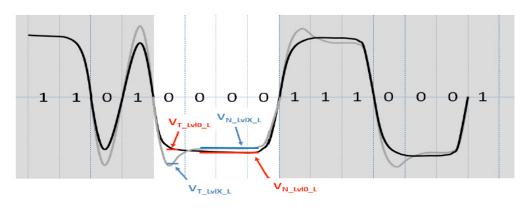

## Source Non Transition Voltage Range Measurement Test 549

Test ID 549 Test Overview 549 Test Conditions for Non Transition Voltage Range Measurement Test 549 Test Setup 550 Measurement Procedure 553 PASS Condition 555 Test References 555 Expected/Observable Results 555

#### Source Peak to Peak Voltage Test 556

Test ID 556 Test Overview 556 Test Conditions for Peak to Peak Voltage Test 556 Test Setup 557 Measurement Procedure 560 PASS Condition 560 Test References 560 Expected/Observable Results 560

## Source Main Link Frequency Compliance Test 561

Test ID 561 Test Overview 561 Test Conditions for Main Link Frequency Compliance Test 561 Test Setup 562 Measurement Procedure 565 PASS Condition 566 Test References 566 Expected/Observable Results 566

#### Source Spread Spectrum Clocking (SSC) Modulation Frequency Test 567

Test ID 567 Test Overview 567 Test Conditions for SSC Modulation Frequency Test 567 Test Setup 568 Measurement Procedure 571 PASS Condition 571 Test References 572 Expected/Observable Results 572

#### Source Spread Spectrum Clocking (SSC) Modulation Deviation Test 573

Test ID 573 Test Overview 573 Test Conditions for SSC Modulation Deviation Test 573 Test Setup 574 Measurement Procedure 577 PASS Condition 578 Test References 578 Expected/Observable Results 578

### Source Spread Spectrum Clocking (SSC) Deviation HF Variation Test (Informative) 579

Test ID 579 Test Overview 579 Test Conditions for SSC Deviation HF Variation Test (Informative) 579 Test Setup 580 Measurement Procedure 583 PASS Condition 583 Test References 584 Expected/Observable Results 584

## Post-Cursor 2 Verification Test (Informative) 585

Test ID 585 585 Test Overview Test Conditions for Post-Cursor 2 Verification Test (Informative) 585 Test Setup 586 589 Measurement Procedure PASS Condition 590 Test References 590 Expected/Observable Results 590

#### Eye Diagram Test (TP3\_EQ) 591

Test ID 591 Test Overview 591 Test Conditions for Eye Diagram Test (TP3\_EQ) 591 Test Setup 592 Measurement Procedure for HBR 595 595 Measurement Procedure for HBR2 PASS Condition 597 Test References 599 599 Expected/Observable Results

#### Total Jitter Test (TP3\_EQ) 600

Test ID 600 Test Overview 600 Test Conditions for Total Jitter Test (TP3\_EQ) 600 Test Setup 601 Measurement Procedure 604 PASS Condition 604 Test References 605 Expected/Observable Results 605

## Deterministic Jitter Test (TP3\_EQ) 606

Test ID 606 Test Overview 606 Test Conditions for Deterministic Jitter Test (TP3\_EQ) 606 Test Setup 607 Measurement Procedure 610 PASS Condition 610 Test References 611 Expected/Observable Results 611

#### Random Jitter Test (TP3\_EQ) 612

Test ID 612 Test Overview 612 Test Conditions for Random Jitter Test (TP3\_EQ) 612 Test Setup 613 Measurement Procedure 616 PASS Condition 616 Test References 616 Expected/Observable Results 616

#### AC Common Mode Test (Informative) 617

Test ID 617 Test Overview 617 Test Conditions for AC Common Mode Test (Informative) 617 Test Setup 618 Measurement Procedure 621 PASS Condition 621 Test References 621 Expected/Observable Results 621

#### Intra-Pair Skew Test (Informative) 622

Test ID 622 Test Overview 622 Test Conditions for Intra-Pair Skew Test (Informative) 622 Test Setup 623 Measurement Procedure 626 PASS Condition 626 Test References 627 Expected/Observable Results 627

## 16 MyDP 1.0 Sink Tests

#### **Overview** 630

Test Point Definition for DisplayPort MyDP 1.0 Sink Tests630Calibration of Stress Signal631Setting Up the DisplayPort Compliance Test Application for MyDP 1.0 Sink Tests632Probing/Connection Set Up for MyDP 1.0 Sink Tests633

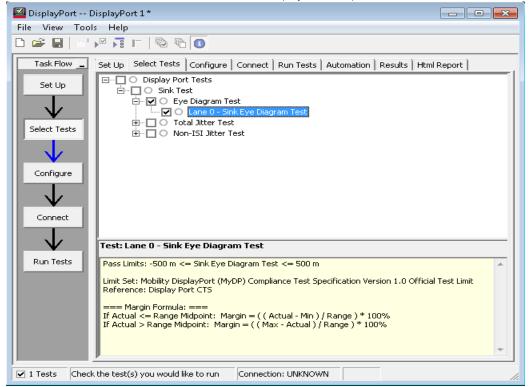

#### Sink Eye Diagram Test 634

Test ID 634 Test Overview 634 Test Conditions for Eye Diagram Test 634 Test Setup 635 Measurement Procedure 638 PASS Condition 638 Test References 640 Expected/Observable Results 640

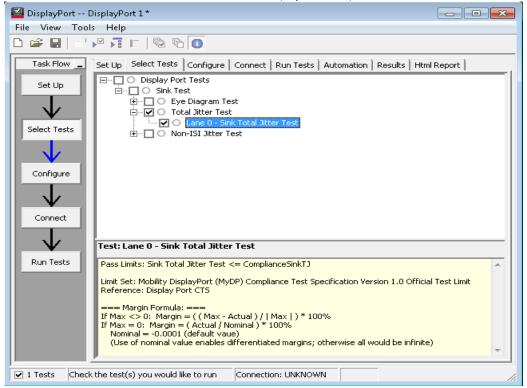

#### Sink Total Jitter Test 641

Test ID 641 Test Overview 641 Test Conditions for Total Jitter Test 641 Test Setup 642 Measurement Procedure 645 PASS Condition 645 Test References 646 Expected/Observable Results 646

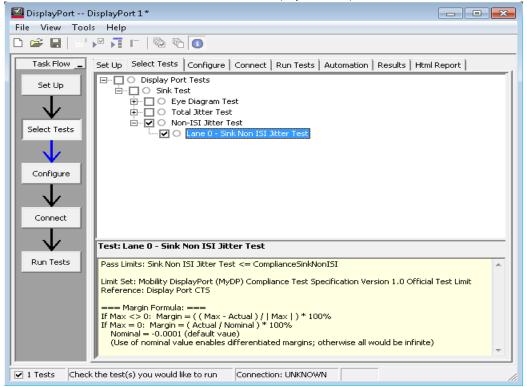

#### Sink Non-ISI Jitter Tests 647

Test ID 647 Test Overview 647 Test Conditions for Non-ISI Jitter Test 647 Test Setup 648 Measurement Procedure 651 PASS Condition 651 Test References 652 Expected/Observable Results 652

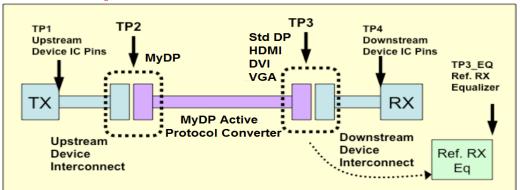

## 17 MyDP 1.0 Cable Tests

#### **Overview** 654

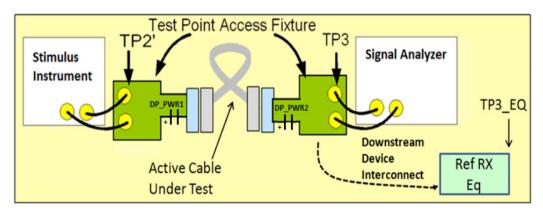

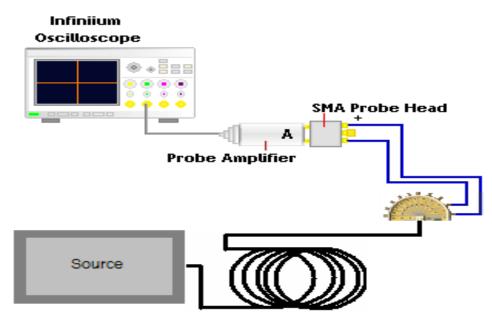

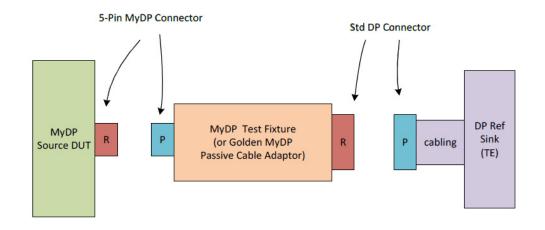

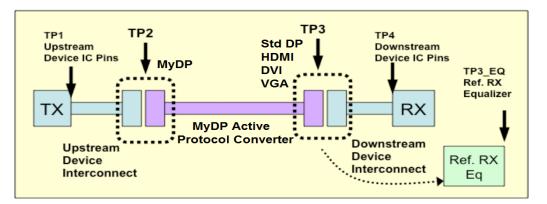

Test Point Definition for MyDP 1.0 Cable Tests654Setting Up the DisplayPort Compliance Test Application for MyDP 1.0 Cable Tests656Probing/Connection Set Up for MyDP 1.0 Cable Tests657

## Cable Eye Diagram Test 658

Test ID 658 Test Overview 658 Test Conditions for Eye Diagram Test 658 Test Setup 659 Measurement Procedure 662 PASS Condition 662 Test References 663 Expected/Observable Results 663

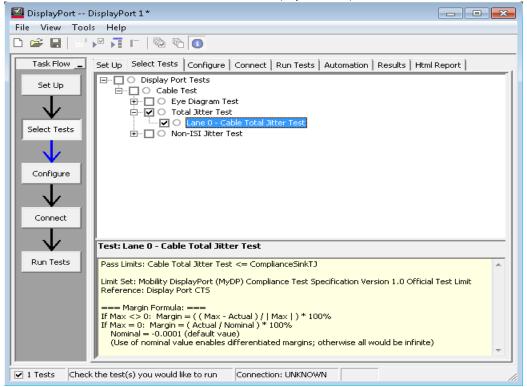

#### Cable Total Jitter Test 664

Test ID 664 Test Overview 664 Test Conditions for Total Jitter Test 664 Test Setup 665 Measurement Procedure 668 PASS Condition 668 Test References 668 Expected/Observable Results 668

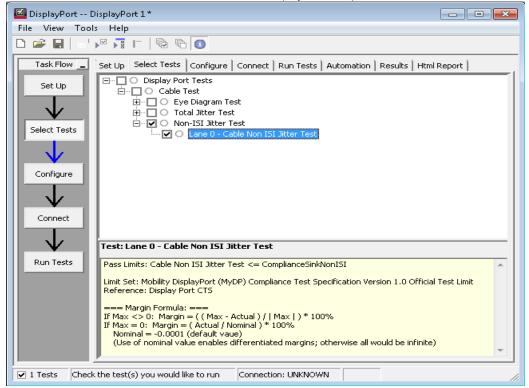

#### Cable Non-ISI Jitter Test 669

Test ID 669 Test Overview 669 Test Conditions for Non-ISI Jitter Test 669 Test Setup 670 Measurement Procedure 673 PPASS Condition 673 Test References 673 Expected/Observable Results 673

## 18 MyDP 1.0 AUX Channel Tests

## **Overview** 676

Test Point for MyDP 1.0 AUX Channel Tests676Setting Up the DisplayPort Compliance Test Application for MyDP 1.0 AUX Channel Tests676

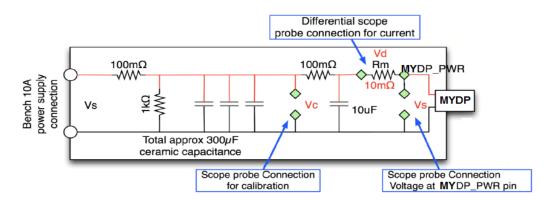

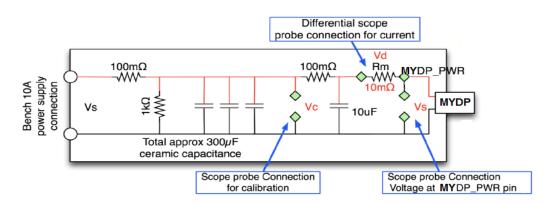

#### Setting Up for AUX PHY and Inrush Tests 679

Probing/Connection Set Up for AUX Channel Tests 685

## AUX Channel Unit Interval Test 687

Test ID 687 Test Overview 687 Test Conditions 687 Measurement Procedure 687 PASS Condition 688 Test References 688 Expected/Observable Results 688

#### AUX Channel Eye Test 689

Test ID 689 Test Overview 689 Test Conditions 689 Measurement Procedure 689 PASS Condition 690 Test References 690 Expected/Observable Results 690

#### AUX Channel Peak-to-Peak Voltage Test 691

Test ID691Test Overview691Test Conditions691Measurement Procedure691PASS Condition692Test References692Expected/Observable Results692

#### AUX Channel Eye Sensitivity Calibration Test 693

Test ID 693 Test Overview 693 Test Conditions 693 Measurement Procedure 693 PASS Condition 694 Test References 694 Expected/Observable Results 694

## AUX Channel Eye Sensitivity Test 695

Test ID695Test Overview695Test Conditions695Measurement Procedure695PASS Condition695Test References696Expected/Observable Results696

## 19 MyDP 1.0 Inrush Tests

### **Overview** 698

Test Point for MyDP 1.0 Inrush Tests698Setting Up the DisplayPort Compliance Test Application for MyDP 1.0 Inrush Tests699

#### Inrush Energy Power Test 701

Test ID701Test Overview701Test Conditions701Measurement Procedure701PASS Condition701Test References701Expected/Observable Results702

#### Inrush Peak Current Test 703

Test ID703Test Overview703Test Conditions703Measurement Procedure703PASS Condition703Test References703Expected/Observable Results704

## 20 SlimPort Source Tests

## **Overview** 706

Test Point Definition for SlimPort Source Tests709Setting Up the DisplayPort Compliance Test Application for SlimPort Source Tests710Probing/Connection Set Up for SlimPort Source Tests712

#### Source Eye Diagram Test 713

Test ID 713 Test Overview 713 Test Conditions for Eye Diagram Test 713 Test Setup 714 Measurement Procedure 717 PASS Condition 717 Test References 718 Expected/Observable Results 719

## Source Total Jitter Test 720

Test ID720Test Overview720Test Conditions for Total Jitter Test720Test Setup721Measurement Procedure724PASS Condition724Test References724Expected/Observable Results724

#### Source Non-ISI Jitter Test 725

Test ID 725 Test Overview 725 Test Conditions for Non-ISI Jitter Test 725 Test Setup 726 Measurement Procedure 729 PASS Condition 729 Test References 729 Expected/Observable Results 729

#### Source Non Pre-Emphasis Level Test 730

Test ID 730 Test Overview 730 Test Conditions for Non Pre-Emphasis Level Test 730 Test Setup 731 Measurement Procedure 734 PASS Condition 736 Test References 737 Expected/Observable Results 737

#### Source Pre-Emphasis Level Test 738

Test ID 738 Test Overview 738 Test Conditions for Pre-Emphasis Level Test 738 Test Setup 739 Measurement Procedure 742 PASS Condition 744 Test References 745 Expected/Observable Results 745

#### Source Non Transition Voltage Range Measurement Test 746

Test ID 746 Test Overview 746 Test Conditions for Non Transition Voltage Range Measurement Test 746 Test Setup 747 Measurement Procedure 750 PASS Condition 752 Test References 752 Expected/Observable Results 752

## Source Peak to Peak Voltage Test 753

Test ID 753 Test Overview 753 Test Conditions for Peak to Peak Voltage Test 753 Test Setup 754 Measurement Procedure 757 PASS Condition 757 Test References 757 Expected/Observable Results 757

#### Source Main Link Frequency Compliance Test 758

Test ID 758 Test Overview 758 Test Conditions for Main Link Frequency Compliance Test 758 Test Setup 759 Measurement Procedure 762 PASS Condition 763 Test References 763 Expected/Observable Results 763

## Source Spread Spectrum Clocking (SSC) Modulation Frequency Test 764

Test ID 764 Test Overview 764 Test Conditions for SSC Modulation Frequency Test 764 Test Setup 765 Measurement Procedure 768 PASS Condition 768 Test References 769 Expected/Observable Results 769

#### Source Spread Spectrum Clocking (SSC) Modulation Deviation Test 770

Test ID770Test Overview770Test Conditions for SSC Modulation Deviation Test770Test Setup771Measurement Procedure774PASS Condition775Test References775Expected/Observable Results775

#### Source Spread Spectrum Clocking (SSC) Deviation HF Variation Test (Informative) 776

Test ID 776 Test Overview 776 Test Conditions for SSC Deviation HF Variation Test (Informative) 776 Test Setup 777 Measurement Procedure 780 PASS Condition 780 Test References 781 Expected/Observable Results 781

#### Post-Cursor 2 Verification Test (Informative) 782

Test ID 782 Test Overview 782 Test Conditions for Post-Cursor 2 Verification Test 782 Test Setup 783 Measurement Procedure 786 PASS Condition 787 Test References 787 Expected/Observable Results 787

#### Eye Diagram Test (TP3\_EQ) 788

Test ID 788 Test Overview 788 Test Conditions for Eye Diagram Test (TP3 EQ) 788 Test Setup 789 792 Measurement Procedure for HBR and HBR25 Measurement Procedure for HBR2 792 794 PASS Condition Test References 796 Expected/Observable Results 796

#### Total Jitter Test (TP3\_EQ) 797

Test ID 797 Test Overview 797 Test Conditions for Total Jitter Test (TP3\_EQ) 797 Test Setup 798 Measurement Procedure 801 PASS Condition 801 Test References 802 Expected/Observable Results 802

## Deterministic Jitter Test (TP3\_EQ) 803

Test ID 803 Test Overview 803 Test Conditions for Deterministic Jitter Test (TP3\_EQ) 803 Test Setup 804 Measurement Procedure 807 PASS Condition 807 Test References 808 Expected/Observable Results 808

#### Random Jitter Test (TP3\_EQ) 809

Test ID 809 Test Overview 809 Test Conditions for Random Jitter Test (TP3\_EQ) 809 Test Setup 810 Measurement Procedure 813 PASS Condition 813 Test References 813 Expected/Observable Results 813

#### AC Common Mode Test (Informative) 814

Test ID 814 Test Overview 814 Test Conditions for AC Common Mode Test (Informative) 814 Test Setup 815 Measurement Procedure 818 PASS Condition 818 Test References 818 Expected/Observable Results 818

## Intra-Pair Skew Test (Informative) 819

Test ID 819 Test Overview 819 Test Conditions for Intra-Pair Skew Test (Informative) 819 Test Setup 820 Measurement Procedure 823 PASS Condition 823 Test References 824 Expected/Observable Results 824

## 21 SlimPort Sink Tests

## **Overview** 826

Test Point Definition for SlimPort Sink Tests826Calibration of Stress Signal827Setting Up the DisplayPort Compliance Test Application for SlimPort Sink Tests828Probing/Connection Set Up for SlimPort Sink Tests829

## Sink Eye Diagram Test 830

Test ID 830 Test Overview 830 Test Conditions for Eye Diagram Test 830 Test Setup 831 Measurement Procedure 834 PASS Condition 834 Test References 836 Expected/Observable Results 836

## Sink Total Jitter Test 837

Test ID 837 Test Overview 837 Test Conditions for Total Jitter Test 837 Test Setup 838 Measurement Procedure 841 PASS Condition 841 Test References 842 Expected/Observable Results 842

## Sink Non-ISI Jitter Test 843

Test ID 843 Test Overview 843 Test Conditions for Non-ISI Jitter Test 843 Test Setup 844 Measurement Procedure 847 PASS Condition 847 Test References 848 Expected/Observable Results 848

## 22 SlimPort Cable Tests

## **Overview** 850

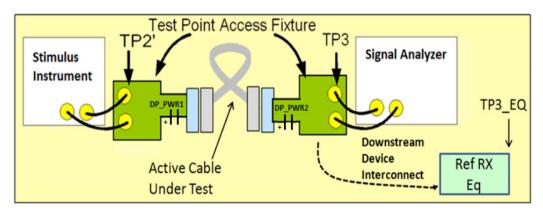

Test Point Definition for SlimPort Cable Tests850Setting Up the DisplayPort Compliance Test Application for SlimPort Cable Tests852Probing/Connection Set Up for SlimPort Cable Tests853

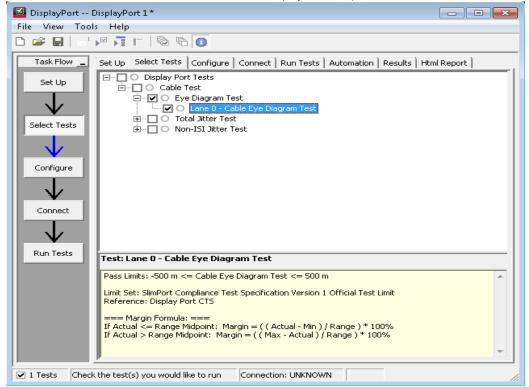

#### Cable Eye Diagram Test 854

Test ID 854 Test Overview 854 Test Conditions for Eye Diagram Test 854 Test Setup 855 Measurement Procedure: 858 PASS Condition 858 Test References 859 Expected/Observable Results 859

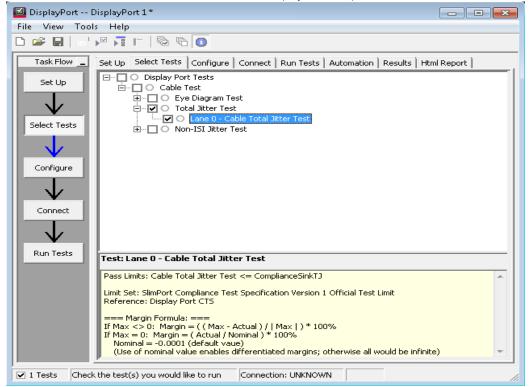

#### Cable Total Jitter Test 860

Test ID 860 Test Overview 860 Test Conditions for Total Jitter Test 860 Test Setup 861 Measurement Procedure 864 PASS Condition 864 Test References 864 Expected/Observable Results 864

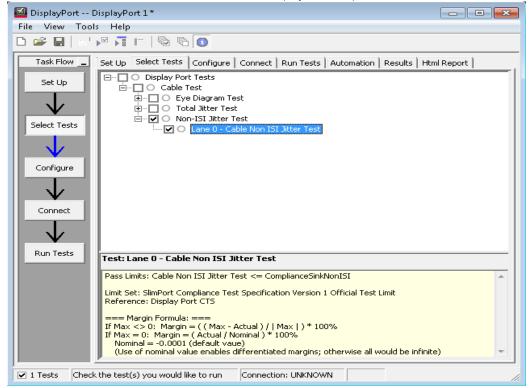

#### Cable Non-ISI Jitter Test 865

Test ID865Test Overview865Test Conditions for Non-ISI Jitter Test865Test Setup866Measurement Procedure869PASS Condition869Test References869Expected/Observable Results869

## 23 SlimPort AUX Channel Tests

#### **Overview** 872

Test Point for SlimPort AUX Channel Tests872Setting Up the DisplayPort Compliance Test Application for SlimPort AUX Channel Tests872

### Setting Up for AUX PHY and Inrush Tests 875

Probing/Connection Set Up for AUX Channel Tests 881

#### AUX Channel Unit Interval Test 883

Test ID 883 Test Overview 883 Test Conditions 883 Measurement Procedure 883 PASS Condition 884 Test References 884 Expected/Observable Results 884

#### AUX Channel Eye Test 885

Test ID 885 Test Overview 885 Test Conditions 885 Measurement Procedure 885 PASS Condition 886 Test References 886 Expected/Observable Results 886

#### AUX Channel Peak-to-Peak Voltage Test 887

Test ID887Test Overview887Test Conditions887Measurement Procedure887PASS Condition888Test References888Expected/Observable Results888

## AUX Channel Eye Sensitivity Calibration Test 889

Test ID889Test Overview889Test Conditions889Measurement Procedure889PASS Condition890Test References890Expected/Observable Results890

## AUX Channel Eye Sensitivity Test 891

Test ID 891 Test Overview 891 Test Conditions 891 Measurement Procedure 891 PASS Condition 891 Test References 892 Expected/Observable Results 892

## 24 SlimPort Inrush Tests

#### **Overview** 894

Test Point894Setting Up the DisplayPort Compliance Test Application for SlimPort Inrush Tests895

#### Inrush Energy Power Test 897

Test ID 897 Test Overview 897 Test Conditions 897 Measurement Procedure 897 PASS Condition 897 Test References 898 Expected/Observable Results 898

## Inrush Peak Current Test 899

Test ID899Test Overview899Test Conditions899Measurement Procedure899PASS Condition899Test References900Expected/Observable Results900

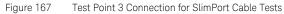

## 25 Calibrating the Infiniium Oscilloscope

| To Run the Self Calibration   | 902                            |     |

|-------------------------------|--------------------------------|-----|

| Internal or Self Calibration  | 903                            |     |

| Probe Calibration and De-ske  | <b>ew</b> 907                  |     |

| Differential SMA Probe Head   | Attenuation/Offset Calibration | 907 |

| Differential SMA Probe Head   | Skew Calibration 911           |     |

| Differential Socketed Probe H | lead Atten/Offset Calibration  | 911 |

| Differential Socketed Probe H | lead Skew Calibration 915      |     |

|                               |                                |     |

## A DisplayPort AUX Channel Cookbook for Tx Automated Test

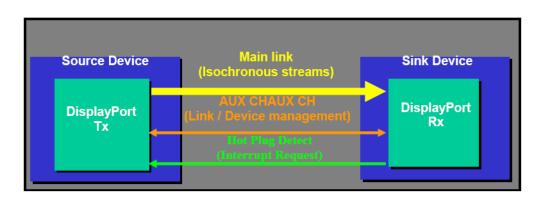

AUX Channel and Hot Plug Detect (HPD) 918

#### **DPTC Controller** 919

## Automated Test Sequence 920

OPTION 1

920

OPTION 2

924

Index

Keysight U7232D DisplayPort Electrical Performance Compliance Test Application

Method of Implementation

# 1 Installing the DisplayPort Electrical Performance Compliance Test Application

Installing the Software / 48 Installing the License Key / 49

If you purchased the U7232D DisplayPort Electrical Performance Compliance Test Application, you need to install the software and license key.

## Installing the Software

- 1 Make sure you have the minimum version of Infiniium oscilloscope software (see the U7232D test application release notes) by choosing **Help>About Infiniium...** from the main menu.

- 2 To obtain the DisplayPort Electrical Performance Compliance Test Application, go to Keysight website: http://www.keysight.com/find/scope-apps-sw.

Figure 1 Keysight website for software Downloads

3 Search the list on this web page for the link to the U7232D DisplayPort Electrical Performance Compliance Test Application. Click the appropriate link and follow the instructions to download and install the application.

## Installing the License Key

- Request a license code from Keysight by following the instructions on the Entitlement Certificate.

You will need the oscilloscope's "Option ID Number", which you can find in the Help>About Infinitum... dialog box.

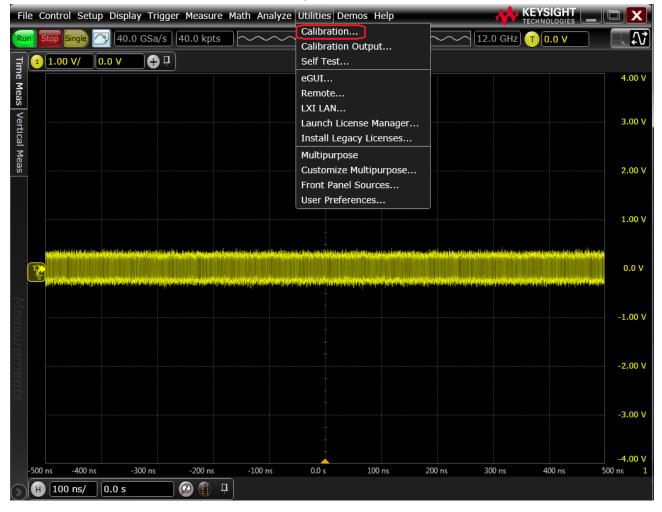

- 2 After you receive your license code from Keysight, choose Utilities>Install Legacy Licenses....

- 3 In the Install Option License dialog, enter your license code and click Install License.

- 4 Click **OK** in the dialog that tells you to restart the Infiniium oscilloscope application software to complete the license installation.

- 5 Click **Close** to close the Install Option License dialog.

- 6 Choose File>Exit.

- 7 Restart the Infiniium oscilloscope application to complete the license installation.

1 Installing the DisplayPort Electrical Performance Compliance Test Application

Keysight U7232D DisplayPort Electrical Performance Compliance Test Application

Method of Implementation

## 2 Preparing to Take Measurements

Calibrating the Oscilloscope / 52 Starting the DisplayPort Electrical Performance Compliance Test Application / 53 Online Help Topics / 55

Before running the DisplayPort automated tests, you must acquire the appropriate test fixtures, and you should calibrate the oscilloscope and probe. After the oscilloscope and probe have been calibrated, you are ready to start the DisplayPort Electrical Performance Compliance Test Application and perform the measurements.

#### 2 Preparing to Take Measurements

## Calibrating the Oscilloscope

If you haven't already calibrated the oscilloscope and probe, see Chapter 25, "Calibrating the Infiniium Oscilloscope.

| NOTE | If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the <b>Utilities&gt;Calibration</b> menu. |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOTE | If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.                                  |

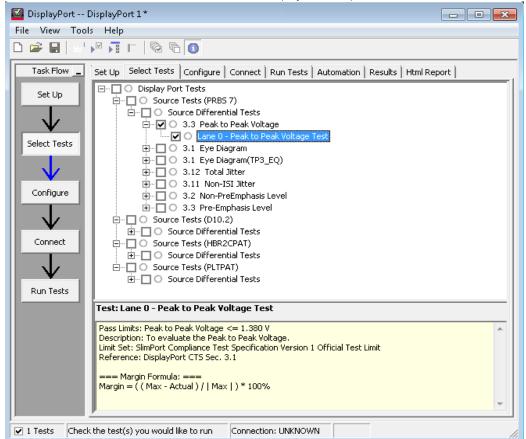

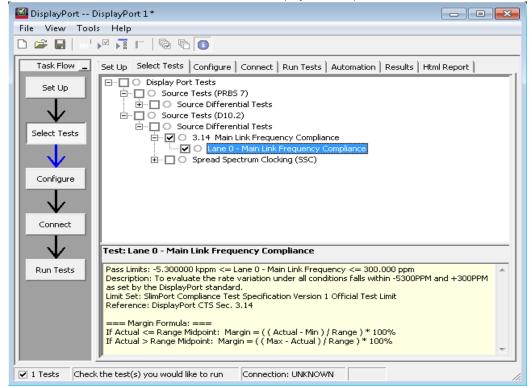

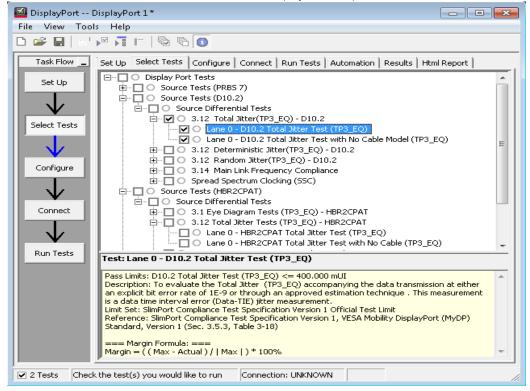

## Starting the DisplayPort Electrical Performance Compliance Test Application

DisplayPort Test App.

Analyze Utilities Demos Help Analysis Browser... Quick Jitter Quick Eye Diagrams Histogram... Mask Test... Automated Test Apps U7232D DisplayPort Test App Measurement Analysis (EZJIT)... Jitter/Noise (EZJIT Complete)... RTEye/Clock Recovery (SDA)... Equalization... CrossTalk...

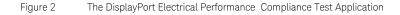

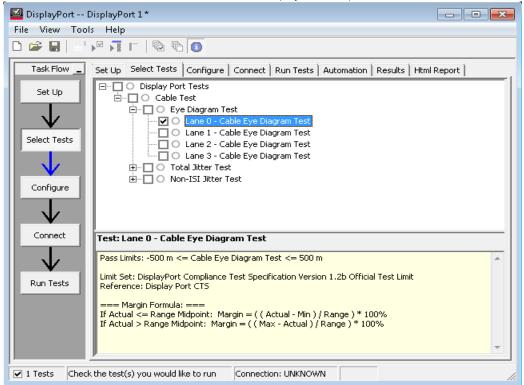

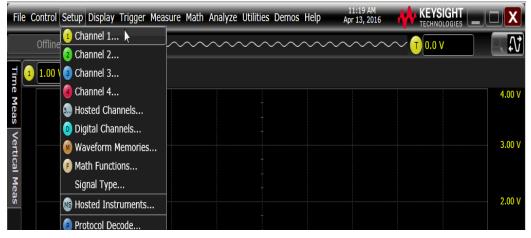

1 From the Infiniium oscilloscope's main menu, choose Analyze>Automated Test Apps>U7232D

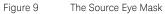

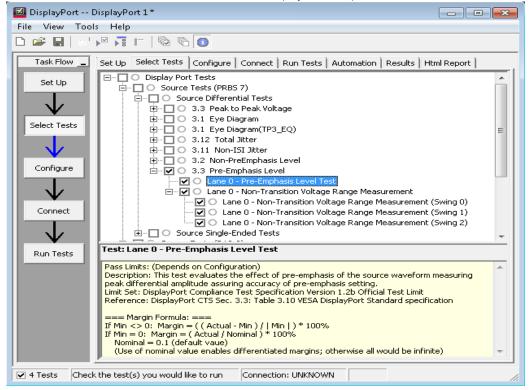

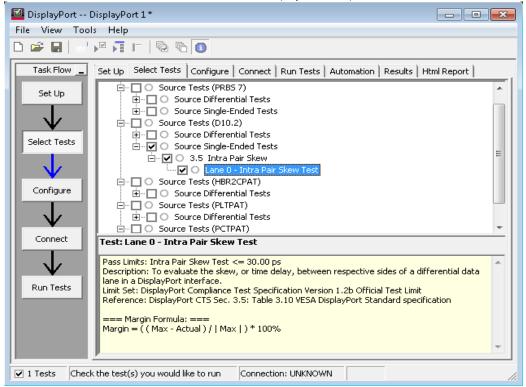

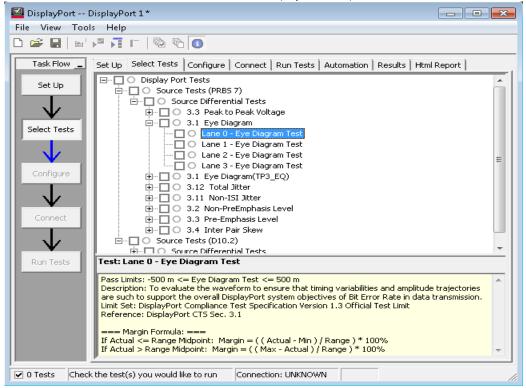

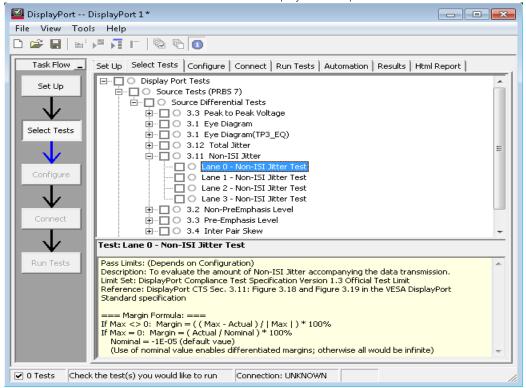

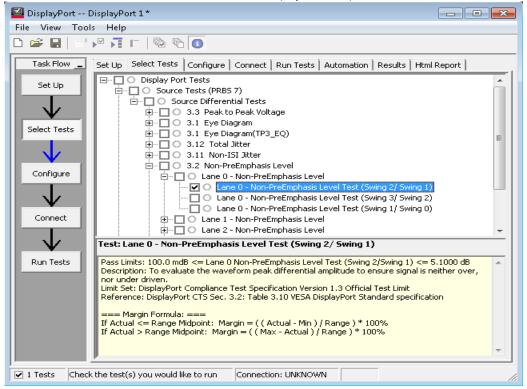

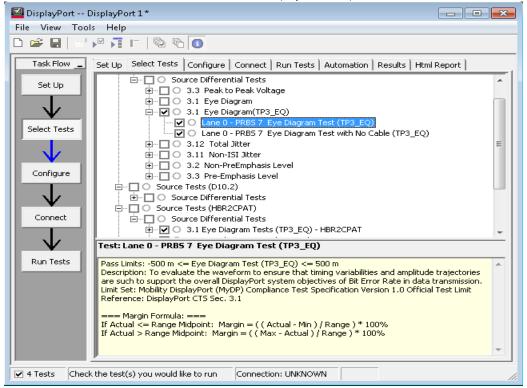

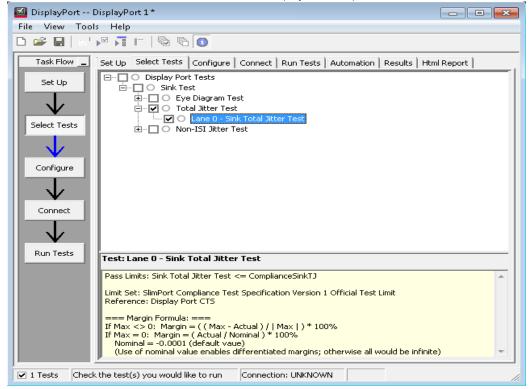

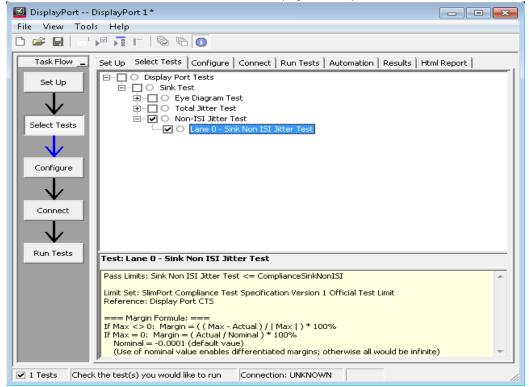

DisplayPort -- DisplayPort 1\* - - -File View Tools Help 🗅 📽 🔚 | 🖬 🟴 ቩ 🗀 | Task Flow Set Up Select Tests | Configure | Connect | Run Tests | Automation | Results | Html Report | DisplayPort Compliance Test Application Set Up Source Tests Setup J **Test Specification** Test Selection Select Tests Physical Layer Tests Test Setup τl C AUX PHY and Inrush Tests Test Setup Incomplete.. O Dual Mode Tests Configure Show Normative Tests Only Connect DisplayPort Test Controller UnigrafDPTC • Enable Automation Configure Script File: C:\Program Files (x86)\Keysight\Infiniium\App Browse Run Tests AUX Channel Controller Mode Standard DP Test Mode Link Training Mode Launch GUI 🗸 0 Tests Follow instructions to describe your test environment Connection: UNKNOWN

## NOTE

If DisplayPort Test does not appear in the Automated Test Apps menu, the DisplayPort Electrical Performance Compliance Test Application has not been installed (see Chapter 1, "Installing the DisplayPort Electrical Performance Compliance Test Application).

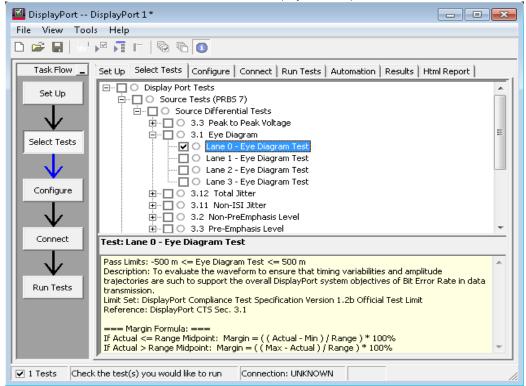

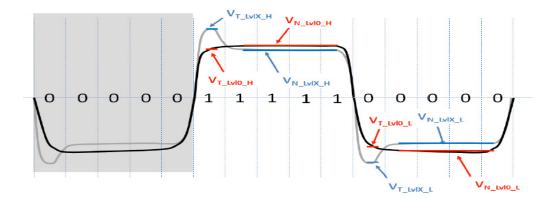

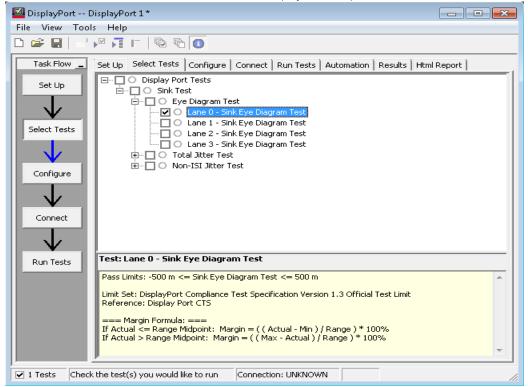

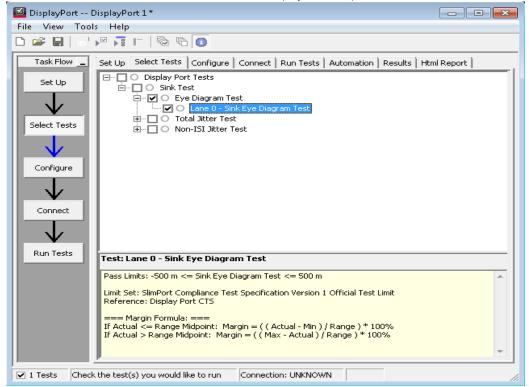

Figure 2 shows the DisplayPort Electrical Performance Compliance Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Tab          | Description                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Up       | Lets you select your setup options. Allows you to setup by device type, test type, fixture type and connection type.                                                                                                                                                       |

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically, so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.     |

| Configure    | Lets you enter information about the device being tested and configure test parameters (like memory depth). This information appears in the HTML report.                                                                                                                   |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Automation   | Enables construction of automated script of commands that drive the functionality of the test application.                                                                                                                                                                 |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

## **Online Help Topics**

For information on using the DisplayPort Electrical Performance Compliance Test Application, see the Online Help (which you can access by choosing **Help>Contents...** from the application's main menu).

The DisplayPort Electrical Performance Compliance Test Application's Online Help describes:

- Starting the DisplayPort Compliance Test Application

- $\cdot~$  To view/minimize the task flow pane

- To view/hide the toolbar

- Creating or Opening a Test Project

- To set load preferences

- Compliance Limits

- To Activate/Refresh Limit Set

- To Create/Edit Limit Set

- Setting Up the Precision Probe/Cable

- Setting Up Switch Matrix

- Setting Up the Test Environment

- Test Setup

- DisplayPort Test Controller

- Selecting Tests

- Configuring Tests

- · Connecting the Oscilloscope to the DUT

- Running Tests

- To select the Store Mode

- To run multiple times

- To send email on pauses or stops

- To pause or stop on events

- · To specify the event

- To set the display preferences

- To set the run preferences

- Automating the Application

- Viewing Results

- To delete trials from the results

- To show reference images and flash mask hits

- To change margin thresholds

- To change the test display order

- To set trial display preferences

- · Viewing/Exporting/Printing the Report

- To export the report

- To print the report

- To set HTML Report preferences

- Understanding the Report

- Saving Test Projects

- To set AutoRecovery preferences

- User Defined Add-Ins

- To install an add-in

- To remove an add-in

- Controlling the Application via a Remote PC

- To check for the App Remote license

- To identify the remote interface version

- To enable the remote interface

- To enable remote interface hints

- Using a Second Monitor

Keysight U7232D DisplayPort Electrical Performance Compliance Test Application

Method of Implementation

# 3 DisplayPort 1.2 Source Tests

Overview / 58 Source Eye Diagram Test / 64 Source Total Jitter Test / 71 Source Non ISI Jitter Test / 76 Source Non Pre-Emphasis Level Test / 81 Source Pre-Emphasis Level Test / 89 Source Non Transition Voltage Range Measurement Test / 97 Source Peak to Peak Voltage Test / 104 Source Inter Pair Skew Test / 109 Source Main Link Frequency Compliance Test / 115 Spread Spectrum Clocking (SSC) Modulation Frequency Test / 121 Spread Spectrum Clocking (SSC) Modulation Deviation Test / 127 Spread Spectrum Clocking (SSC) Deviation HF Variation Test (Informative) / 133 Source Post-Cursor 2 Verification Test (Informative) / 139 Source Eye Diagram Test (TP3\_EQ) / 145 Source Total Jitter Test (TP3\_EQ) / 154 Source Deterministic Jitter Test (TP3\_EQ) / 160 Source Random Jitter Test (TP3\_EQ) / 166 Source AC Common Mode Test (Informative) / 171 Source Intra-Pair Skew Test (Informative) / 176

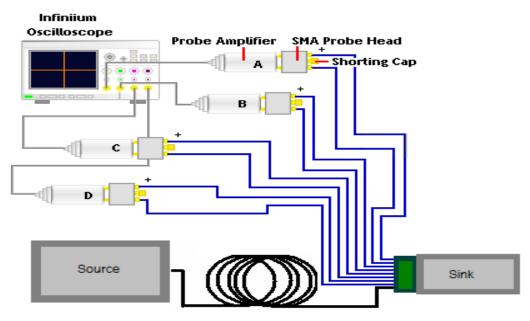

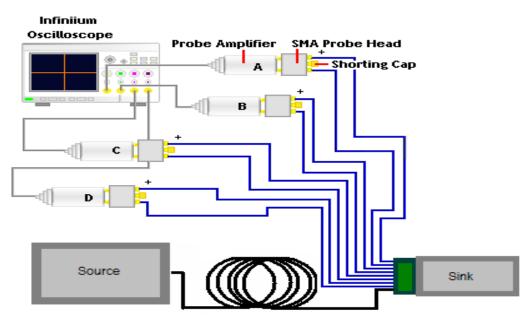

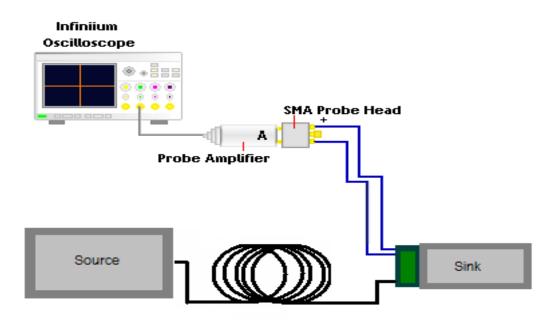

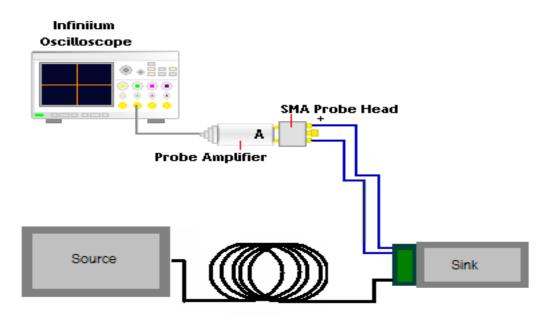

This section provides the guidelines for source eye diagram differential tests using a Keysight 13 GHz or greater Infiniium oscilloscope, 1168A or 1169A probes, and the DisplayPort Electrical Performance Compliance Test Application.

#### 3 DisplayPort 1.2 Source Tests

## Overview

This section describes the normative and informative main link physical layer tests for compliance verification of DisplayPort 1.2 source, sink and cable devices.

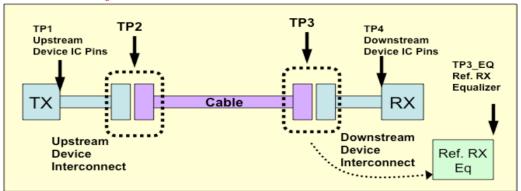

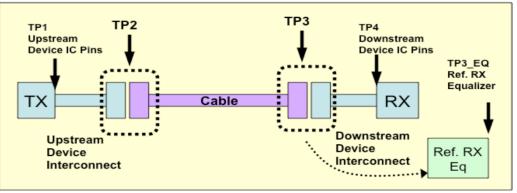

#### Test Point Definition for DisplayPort 1.2 (1.2b) Tests

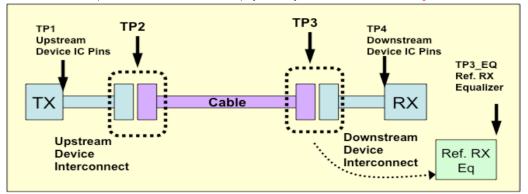

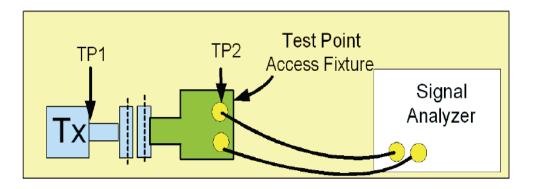

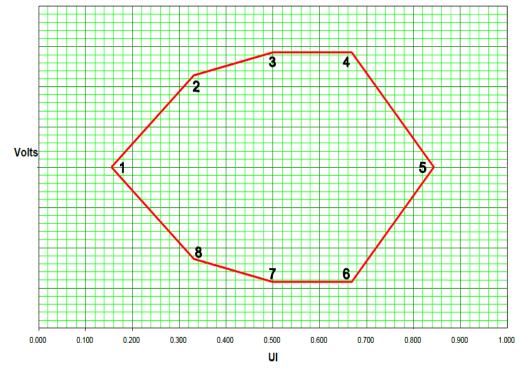

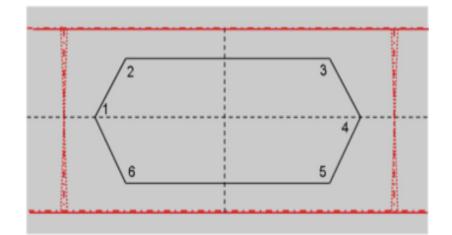

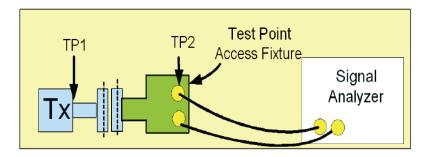

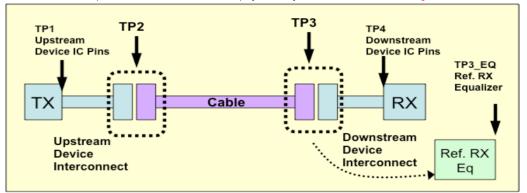

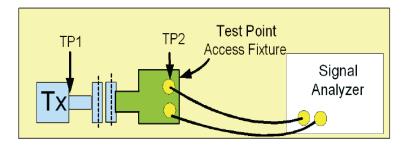

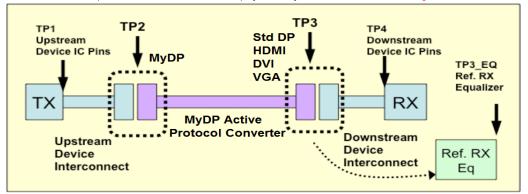

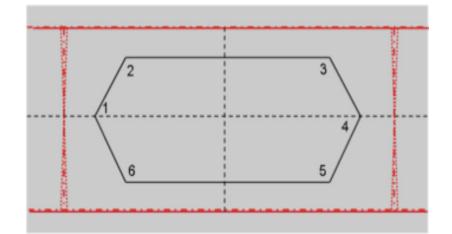

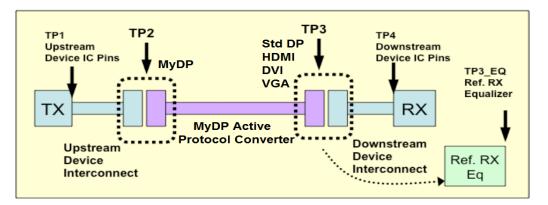

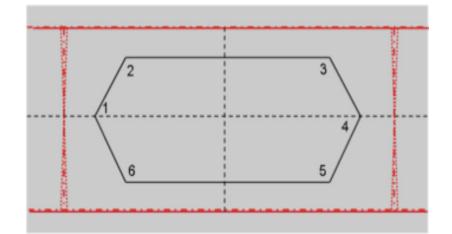

Five different test points are identified for the physical layer measurement. See Figure 3

Table 1 defines the Test Points used for various DisplayPort 1.2 Tests:

#### Table 1 Test Points for DisplayPort Tests

| Test Point | Description                                                                                                                                                                                                                                                                                           |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP1        | At the pins of the Transmitter Device                                                                                                                                                                                                                                                                 |

| TP2        | At the test interface on a test access fixture as close as possible to the DP mated connection to a Source device                                                                                                                                                                                     |

| TP3        | At the test interface on a test access fixture as close as possible to the DP mated connection to a Sink device                                                                                                                                                                                       |

| TP3_EQ     | <ul> <li>At TP3, when a defined cable model with equalizer is applied. There are two defined cable models:</li> <li>Worst Cable Model as defined in VESA DisplayPort 1.2a Standard,</li> <li>Zero length, zero loss cable. The equalizer is also defined in VESA DisplayPort 1.2a Standard</li> </ul> |

| TP4        | At the pins of a receiving device                                                                                                                                                                                                                                                                     |

#### Cable Models

The two cable models defined in VESA DisplayPort 1.2a Standard are:

- 1 Worst Case Cable Model—To achieve the TP3\_EQ signal with the worst case cable model:

- Acquire the signal at TP2.

- Embed the TP2 signal with a "worst case" HBR cable model using an InfiniiSim Waveform Transformation Toolset software to emulate the insertion loss as defined in Figure 4-10 of the VESA DisplayPort 1.2a Standard.

- For the DisplayPort Compliance Test Application, the "*CIC\_revOp6.s4p*" cable model transfer function is used.

- Finally, apply the HBR or HBR2 equalization using the Serial Data Equalization software as defined in Figure 3-40 (for HBR) and Figure 3-41 (for HBR2) of the VESA DisplayPort 1.2a Standard.

- 2 Zero Length Cable Model—To achieve the TP3\_EQ signal with the zero length cable model:

- Acquire the signal at TP2.

- No cable model is embedded for the Zero Length cable model.

- Finally, apply the HBR or HBR2 equalization using the Serial Data Equalization software as defined in Figure 3-40 (for HBR) and Figure 3-41 (for HBR2) of the VESA DisplayPort 1.2a Standard.

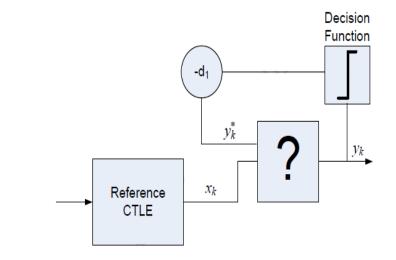

#### Equalization

When equalization is required, use the CTLE (Continuous Time Linear Equalization) transfer function, as given in Figure 3-40 (for HBR) and Figure 3-41 (for HBR2) of the VESA DisplayPort 1.2a Standard.

For main link, use the CTLE model with the following transfer function for HBR (2.7 Gbps):

#### The HBR Reference Equalizer transfer function is given by

$$H(s) = \frac{\omega_{p1}\omega_{p2}}{\omega_z} \cdot \frac{s + \omega_z}{(s + \omega_{p1})(s + \omega_{p2})}$$

which has magnitude given by

$$|H(j\omega)| = \frac{\omega_{p1}\omega_{p2}}{\omega_z} \cdot \frac{\sqrt{\omega^2 + \omega_z^2}}{\sqrt{\omega^2 + \omega_{p1}^2} \cdot \sqrt{\omega^2 + \omega_{p2}^2}}$$

where

$$\begin{split} \omega_{z} &= 2\pi (0.725 \times 10^{9}) \\ \omega_{p1} &= 2\pi (1.35 \times 10^{9}) \\ \omega_{p2} &= 2\pi (2.5 \times 10^{9}) \end{split}$$

Figure 4 Transfer Function of the CTLE model for HBR

#### Table 2 CTLE Model for HBR

| CTLE Parameter   | Worst Case Cable Model | Zero Length Cable Model |

|------------------|------------------------|-------------------------|

| Gain             | 1.0                    | 1.0                     |

| Zero Frequency   | 0.725 GHz              | 0.725 GHz               |

| Pole 1 Frequency | 1.35 GHz               | 1.35 GHz                |

| Pole 2 Frequency | 2.5 GHz                | 2.5 GHz                 |

For main link, use the CTLE model with the following transfer function for HBR2 (5.4 Gbps):

The HBR2 Reference Equalizer transfer function is given by

$$H(s) = \frac{\omega_{p1}\omega_{p2}\omega_{p3}}{\omega_z} \cdot \frac{s + \omega_z}{(s + \omega_{p1})(s + \omega_{p2})(s + \omega_{p3})}$$

which has magnitude given by

$$|H(j\omega)| = \frac{\omega_{p1}\omega_{p2}\omega_{p3}}{\omega_z} \cdot \frac{\sqrt{\omega^2 + \omega_z^2}}{\sqrt{\omega^2 + \omega_{p1}^2} \cdot \sqrt{\omega^2 + \omega_{p2}^2} \cdot \sqrt{\omega^2 + \omega_{p3}^2}}$$

where

$\omega z = 2\pi (0.64 \times 10^9)$  for upstream device compliance

and

$$\omega p 1 = 2\pi (2.7 \times 10^9)$$

$\omega p 2 = 2\pi (4.5 \times 10^9)$

$\omega p 3 = 2\pi (13.5 \times 10^9)$

Figure 5 Transfer Function of the CTLE model for HBR2

#### Table 3 CTLE Model for HBR2

| CTLE Parameter   | Worst Case Cable Model | Zero Length Cable Model |

|------------------|------------------------|-------------------------|

| Gain             | 1.0                    | 1.0                     |

| Zero Frequency   | 0.64 GHz               | 0.64 GHz                |

| Pole 1 Frequency | 2.7 GHz                | 2.7 GHz                 |

| Pole 2 Frequency | 4.5 GHz                | 4.5 GHz                 |

| Pole 3 Frequency | 13.5 GHz               | 13.5 GHz                |

#### **Clock Recovery**

When Clock Recovery is required, the clock recovery technique follows the definition of the receiver PLL as defined in Section 3.5.3.5 of the VESA DisplayPort 1.2a Standard. For main link, use the second-order clock recovery function with a closed loop tracking bandwidth and damping factor, with respect to the PRBS7 pattern, as shown in Table 4:

#### Table 4 Main Link Second-Order Clock Recovery Function

| Bit Rate        | Band wid th | Damping Factor |

|-----------------|-------------|----------------|

| HBR2 (5.4 Gbps) | 10 MHz      | 1.00           |

| HBR (2.7 Gbps)  | 10 MHz      | 1.51           |

| RBR (1.62 Gbps) | 5.4 MHz     | 1.51           |

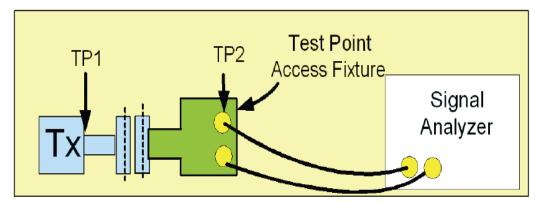

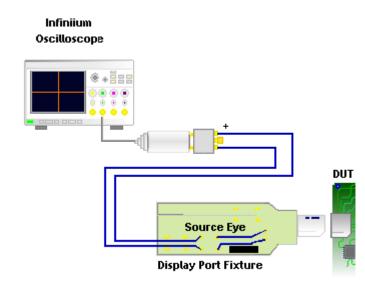

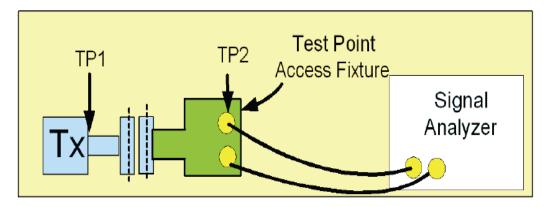

Test Point Definition for DisplayPort 1.2 (1.2b) Source Tests

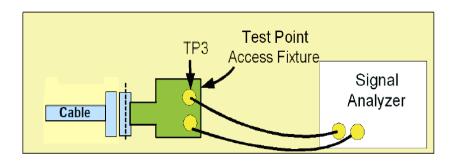

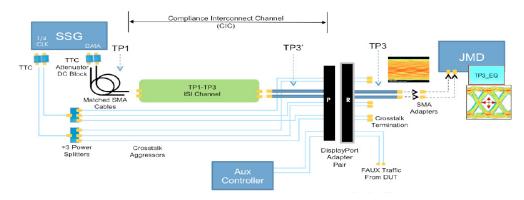

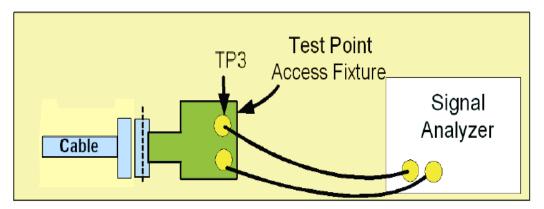

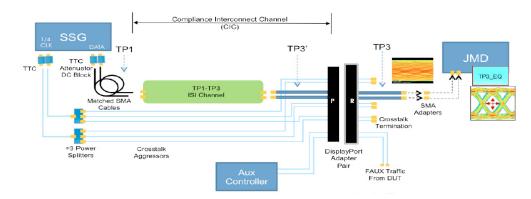

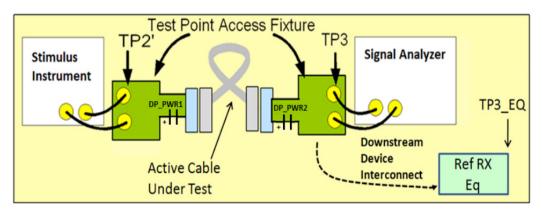

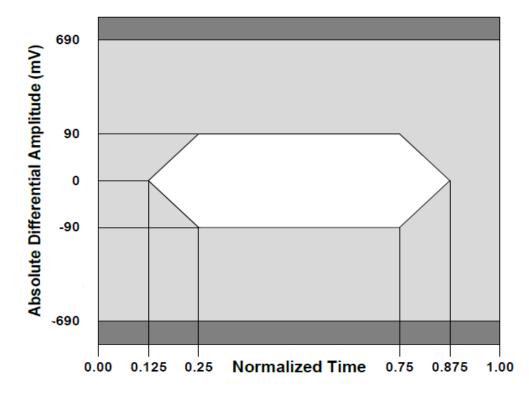

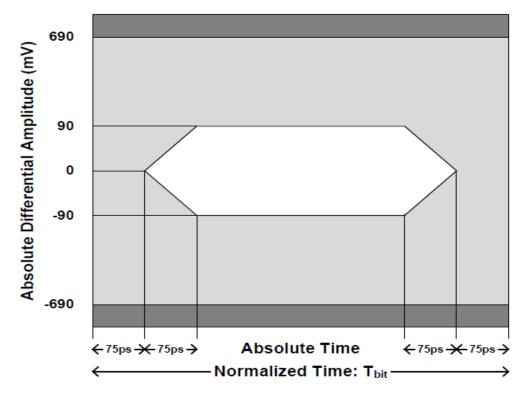

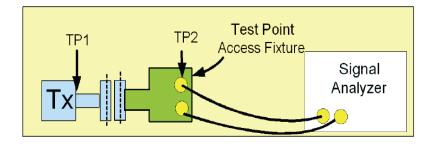

Test the Source DUT at Test Point 2 (TP2) as shown in Figure 6. Unless specifically stated under the Test Conditions, all supported lanes for the DUT shall be evaluated:

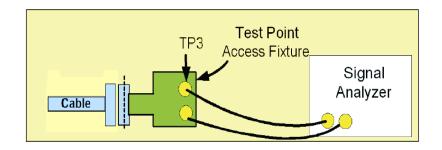

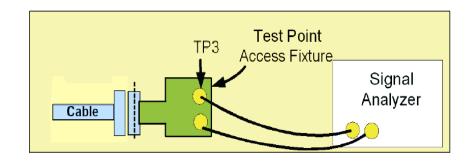

Figure 6 Test Point 2 Connection for DisplayPort 1.2 Source Tests

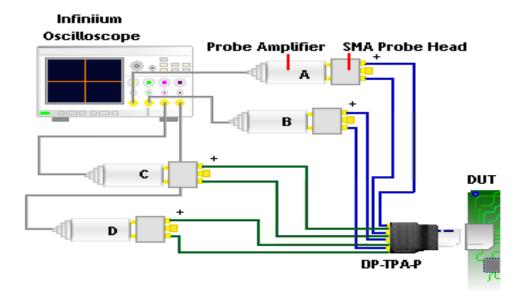

Table 5 defines the test point fixtures and instruments used for DisplayPort 1.2 (1.2b) Source Tests:

| Table 5 | Test Point Fixtures and | Instruments fo | or DisplayPort 1 | .2 Source Tests |